双通道数据采集系统设计Verilog代码VIVADO仿真

采用FPGA为控制核心,基于EDK-SDUST-EEC-EDA实验系统平台或其他硬件平台,设计一套ADC双通道数据采集系统,实现模拟量的采集、传输与显示,系统需具备阈值触发和按键触发、系统状态显示等功能。按下K2键,启动2通道采集;2.数据采集系统状态显示,通过LED灯显示采集系统的当前状态,例如D0亮表示单通道采集状态;3.设置阈值触发功能,模拟量超过一定的阈值(0.2V左右),数据采集系统开始

名称:双通道数据采集系统设计Verilog代码VIVADO仿真(文末获取)

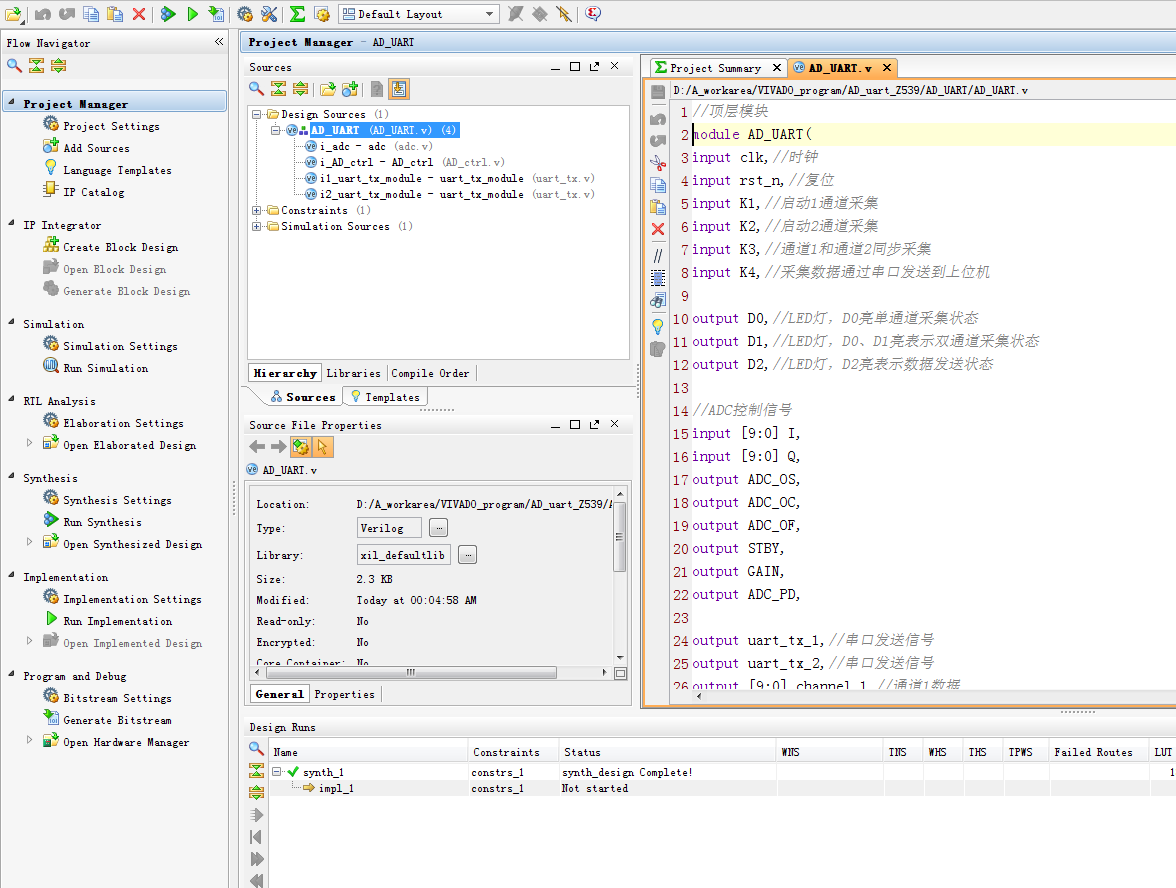

软件:VIVADO

语言:Verilog

代码功能:

采用FPGA为控制核心,基于EDK-SDUST-EEC-EDA实验系统平台或其他硬件平台,设计一套ADC双通道数据采集系统,实现模拟量的采集、传输与显示,系统需具备阈值触发和按键触发、系统状态显示等功能。系统组成包括但不局限于:主控电路、电源电路、存储电路、显示电路、LED灯指示电路、保护电路等。

一、系统功能需达到下列要求:

1.通过按键可以控制数据采集系统的启动、停止以及数据发送,例如:按下K1键,启动1通道采集;按下K2键,启动2通道采集;按下K3键,通道1和通道2同步采集;按下K4键,采集数据通过串口发送到上位机(注意区别2个通道的数据);按下Reset键,系统复位;其余功能可以自行设置定义。

2.数据采集系统状态显示,通过LED灯显示采集系统的当前状态,例如D0亮表示单通道采集状态;D0、D1亮表示双通道采集状态;D0、D1灭、D2亮表示数据发送状态,数据传输完毕D2灯灭;其余功能可以自行设置定义。

3.设置阈值触发功能,模拟量超过一定的阈值(0.2V左右),数据采集系统开始采集,达到设置的采样时间(1s)后结束采样;

4.模拟量显示功能,通过串口调试助手、示波器或者借助其余软件(Matlab)显示采集的真实物理量/曲线;

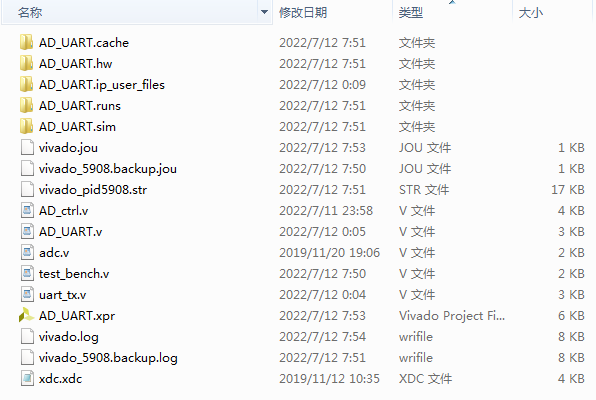

1. 工程文件

2. 程序文件

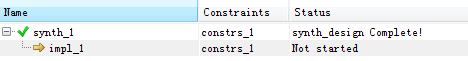

3. 程序编译

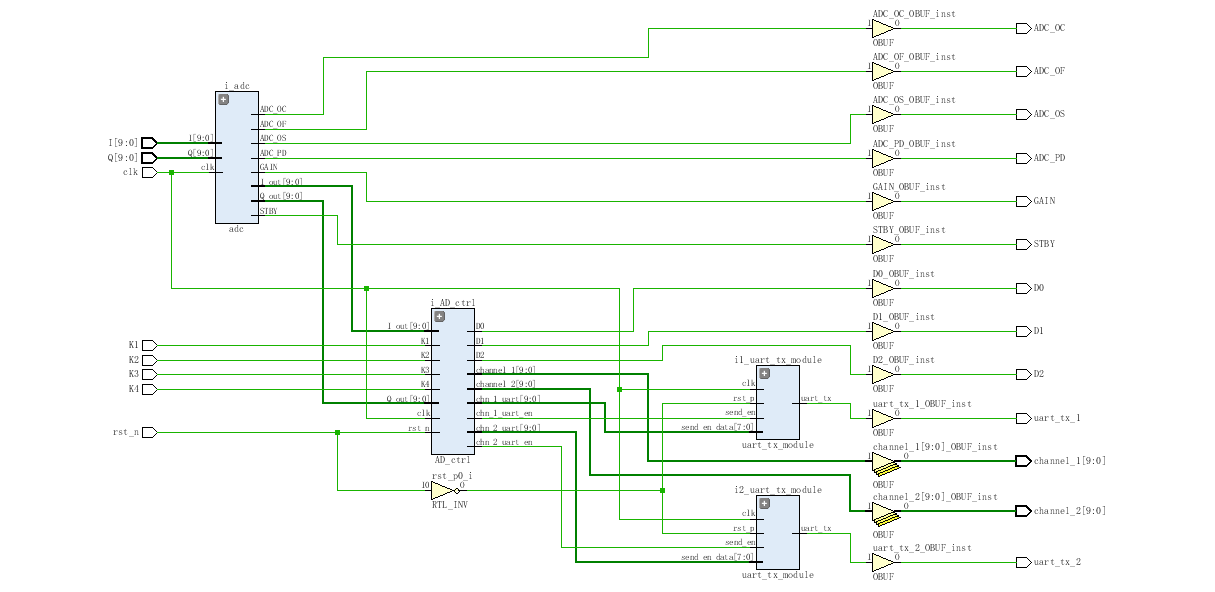

4. RTL图

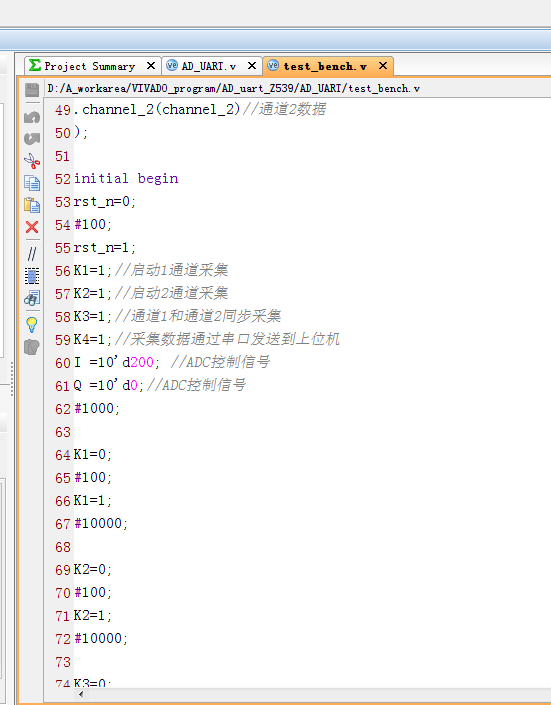

5. Testbench

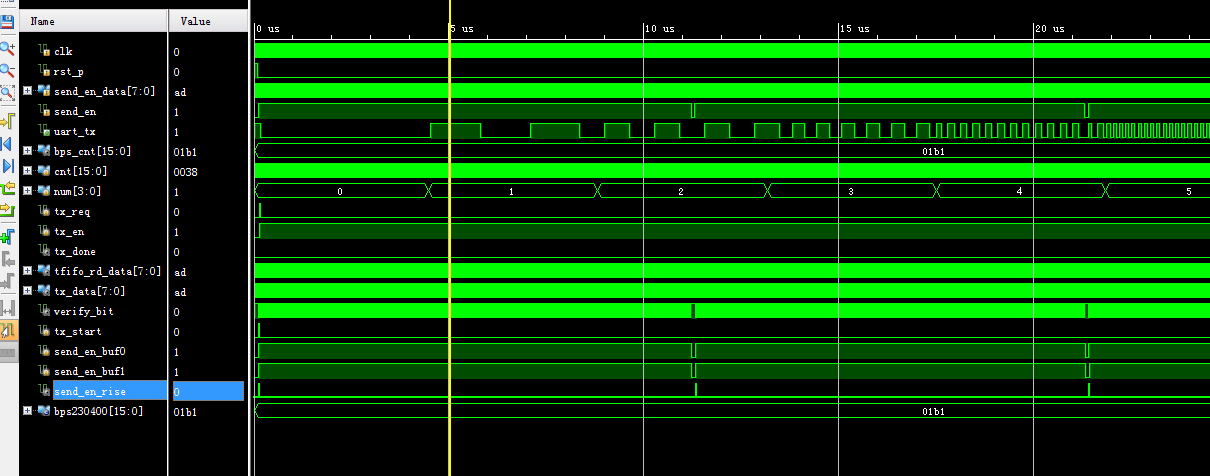

6. 仿真图

整体仿真图

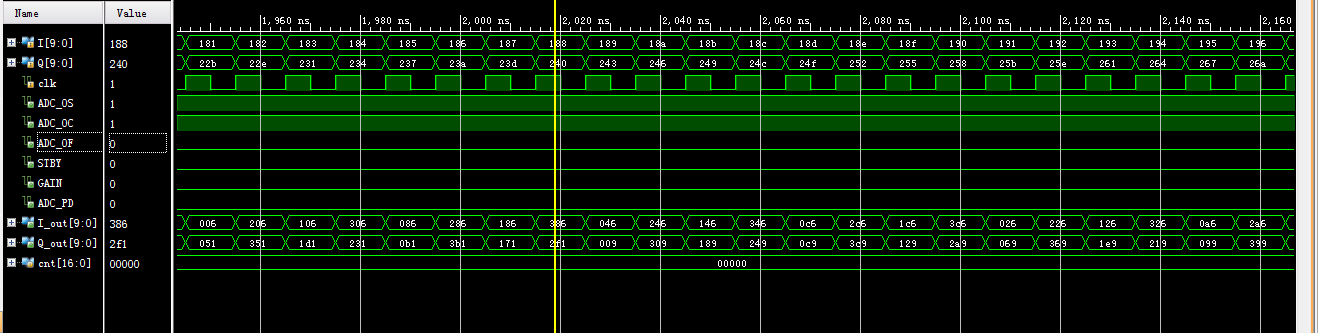

Adc模块

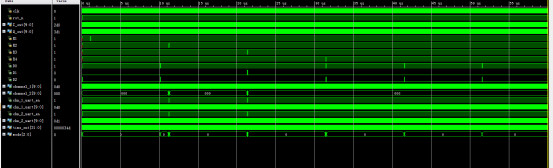

AD按键控制模块

串口发送模块

部分代码展示:

//AD控制模块 module AD_ctrl( input clk,//时钟 input rst_n,//复位 input [9:0] I_out,//通道1数据 input [9:0] Q_out,//通道2数据 input K1,//启动1通道采集 input K2,//启动2通道采集 input K3,//通道1和通道2同步采集 input K4,//采集数据通过串口发送到上位机 output reg D0,//LED灯,D0亮单通道采集状态 output reg D1,//LED灯,D0、D1亮表示双通道采集状态 output reg D2,//LED灯,D2亮表示数据发送状态 output reg [9:0] channel_1,//通道1数据 output reg [9:0] channel_2,//通道2数据 output reg chn_1_uart_en,//串口1发送使能 output reg [9:0] chn_1_uart,//串口1发送数据 output reg chn_2_uart_en,//串口2发送使能 output reg [9:0] chn_2_uart //串口2发送数据 ); //AD串口电压为1.4V //根据公式:1.4v/4096=0.2V/x //x=585 reg [31:0] time_cnt=32'd0; reg [2:0] mode=3'd7; //模式控制 always@(posedge clk or negedge rst_n) if(!rst_n) mode<=2'd7;//复位,7为无效模式 else if(K1==0)//按键触发,启动1通道采集 mode<=2'd0;//1通道采集 else if(K2==0)//按键触发,启动2通道采集 mode<=2'd1;//2通道采集 else if(K3==0)//按键触发,通道1和通道2同步采集 mode<=2'd2;//通道1和通道2同步采集 else if(K4==0)//按键触发,采集数据通过串口发送到上位机 mode<=2'd3; else if(I_out>10'd585 || Q_out>10'd585)//预置触发,判断大于0.2.自动采集1秒 mode<=2'd4; else if(time_cnt>=32'd1000)//计时1秒--仿真将100_000_000改小为1000 mode<=2'd7;//回到无效状态 //1秒计时 always@(posedge clk or negedge rst_n) if(!rst_n) time_cnt<=32'd0; else if(mode==2'd4) time_cnt<=time_cnt+1;//计时 else time_cnt<=32'd0;

源代码

点击下方的公众号卡片获取

魔乐社区(Modelers.cn) 是一个中立、公益的人工智能社区,提供人工智能工具、模型、数据的托管、展示与应用协同服务,为人工智能开发及爱好者搭建开放的学习交流平台。社区通过理事会方式运作,由全产业链共同建设、共同运营、共同享有,推动国产AI生态繁荣发展。

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)