基于FPGA的使用booth、移位、并行算法实现乘法器Verilog代码Quartus仿真

代码功能:使用booth、移位、并行算法实现乘法器1、使用三种方法设计8位乘法器2、使用booth算法实现3、使用移位相加算法实现4、使用并行相乘算法实现

·

名称:基于FPGA的使用booth、移位、并行算法实现乘法器Verilog代码Quartus仿真(文末获取)

软件:Quartus

语言:Verilog

代码功能:

使用booth、移位、并行算法实现乘法器

1、使用三种方法设计8位乘法器

2、使用booth算法实现

3、使用移位相加算法实现

4、使用并行相乘算法实现

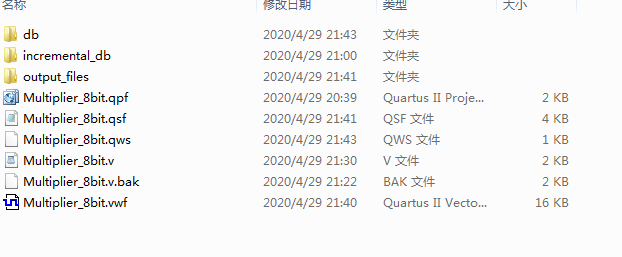

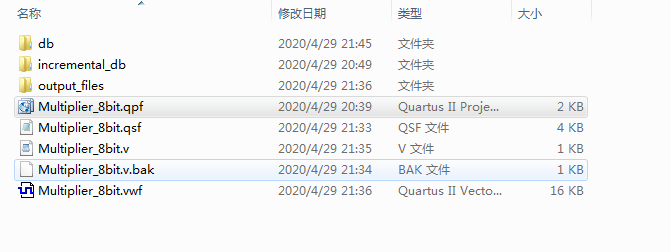

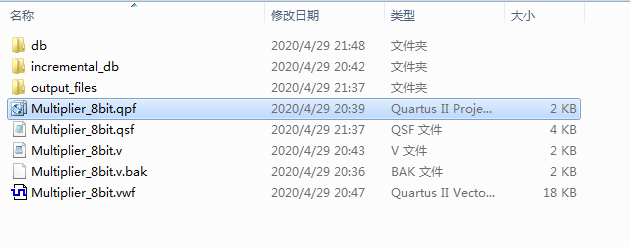

1. 工程文件

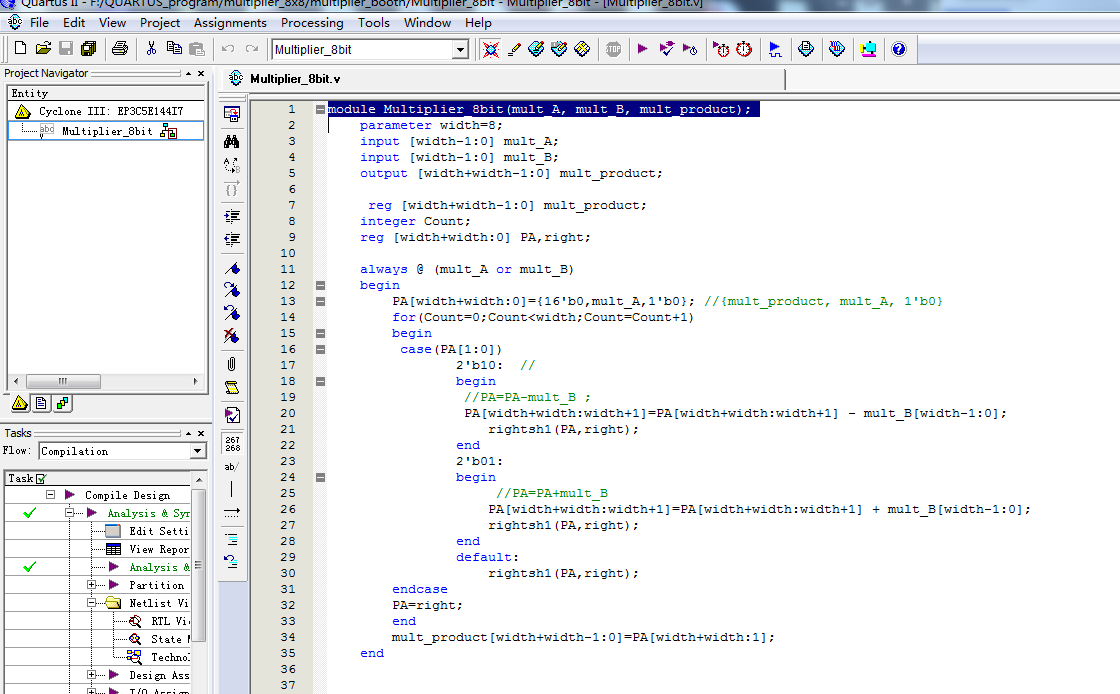

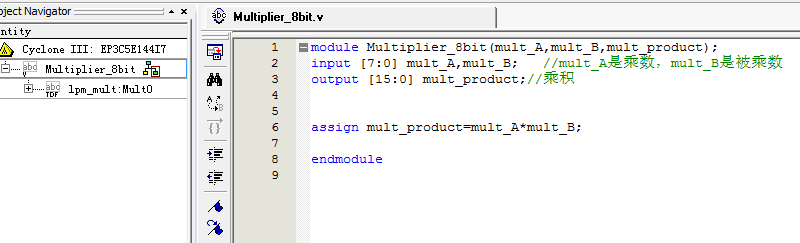

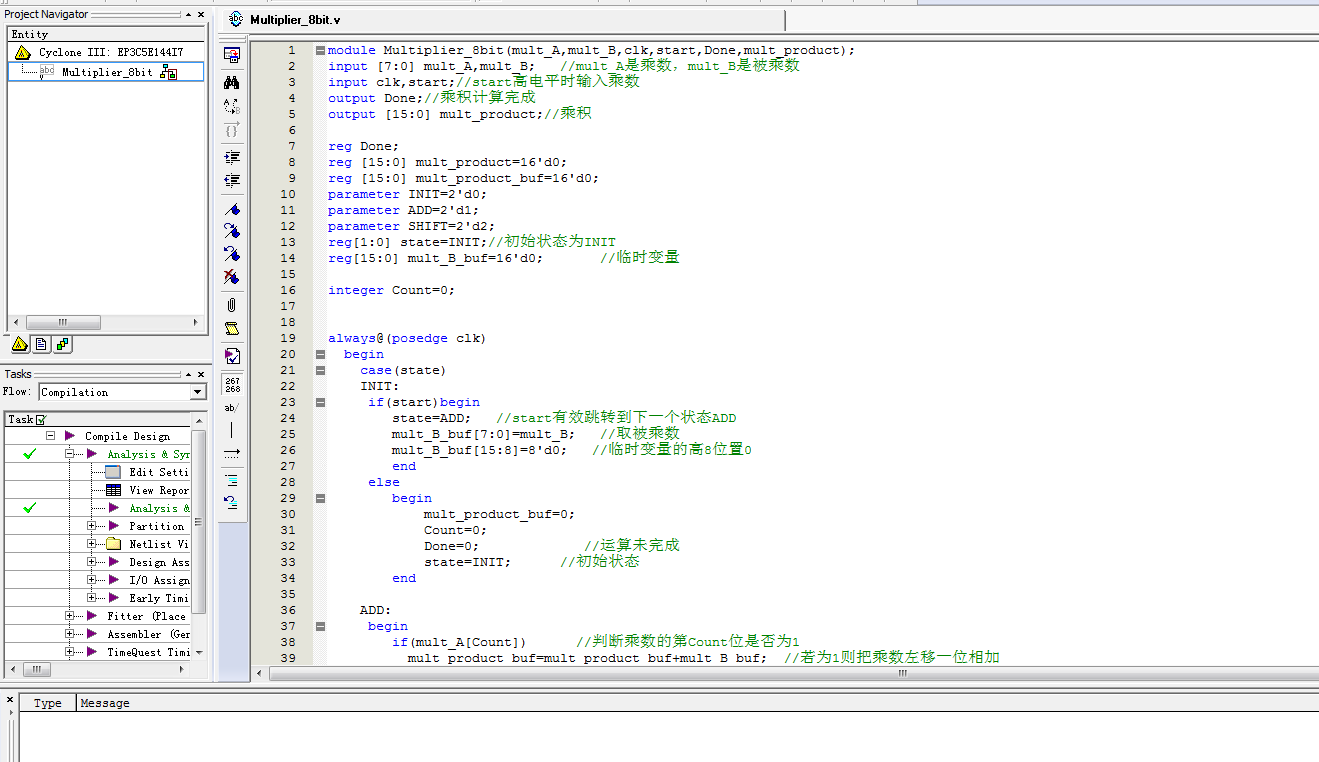

2. 程序文件

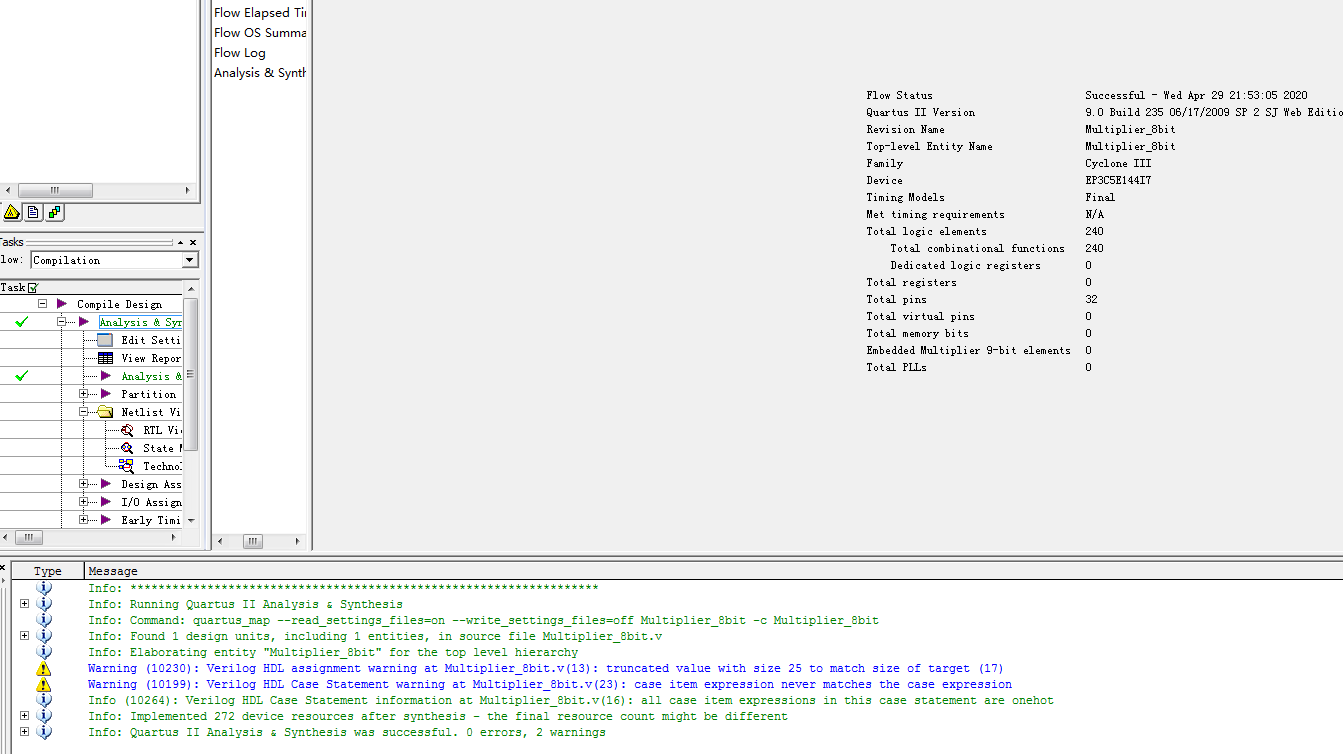

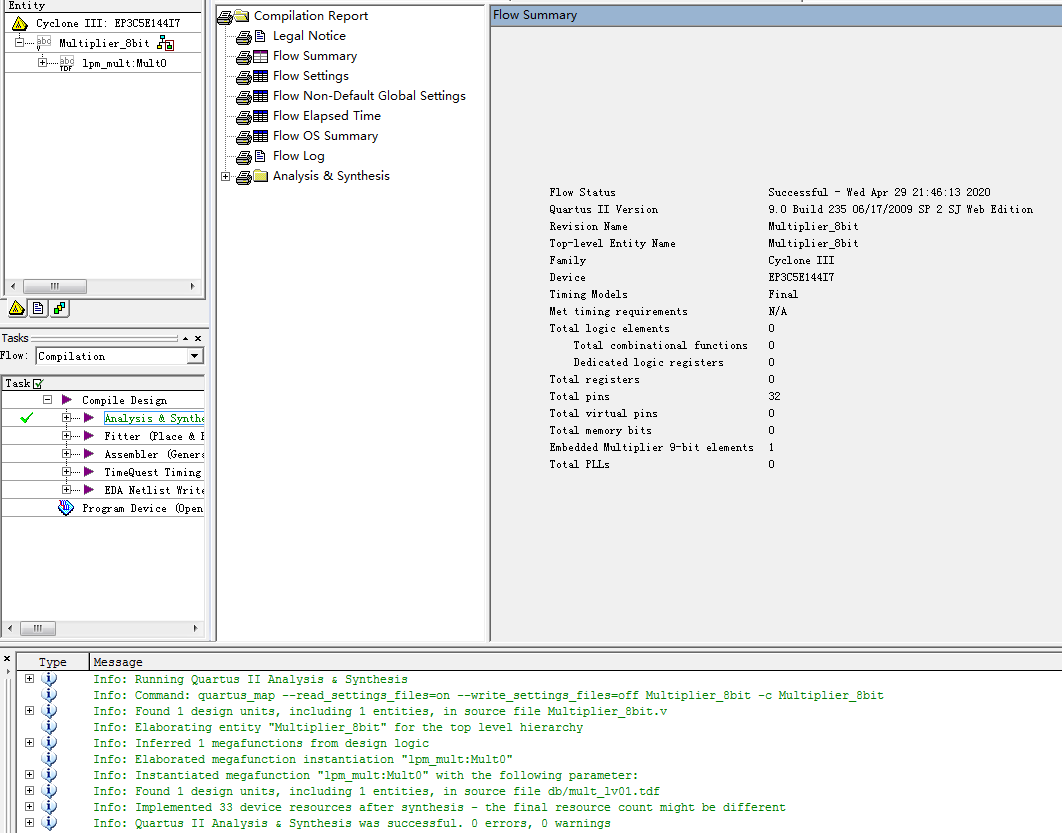

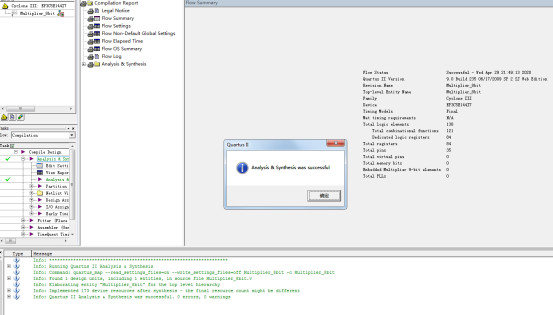

3. 程序编译

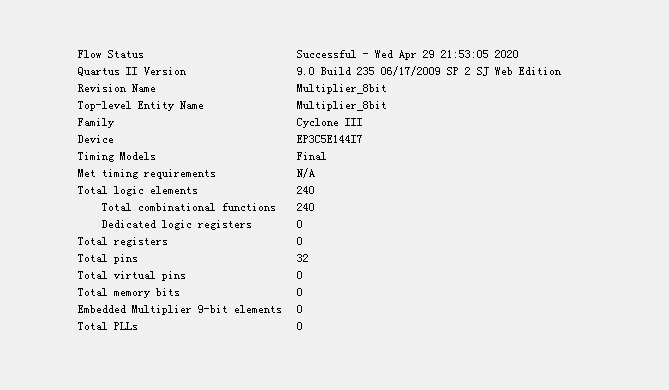

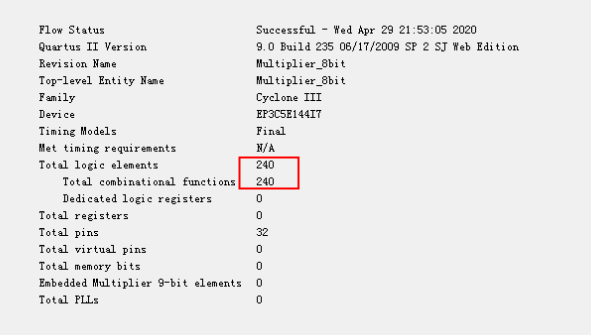

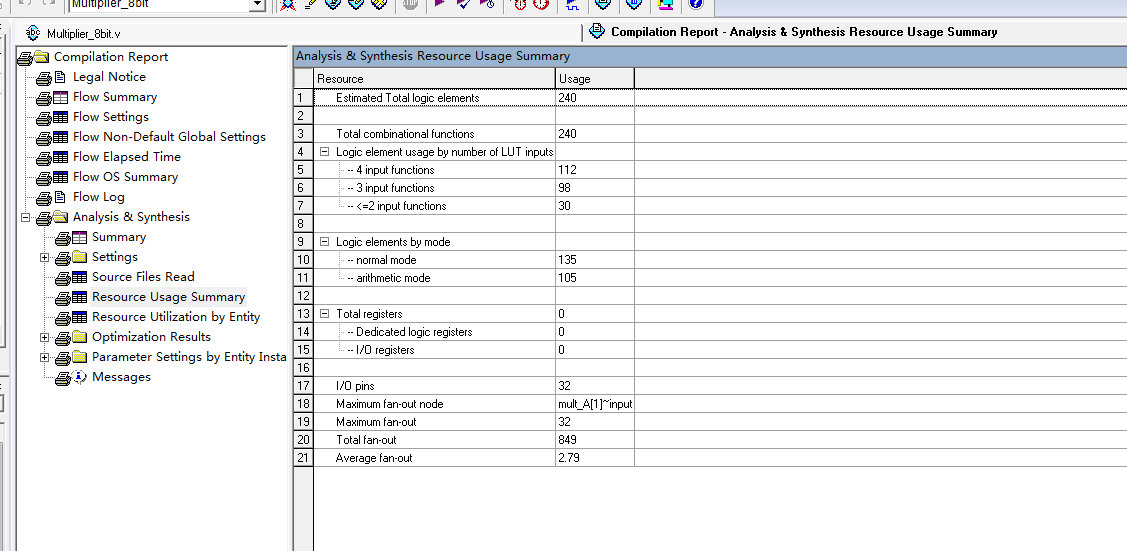

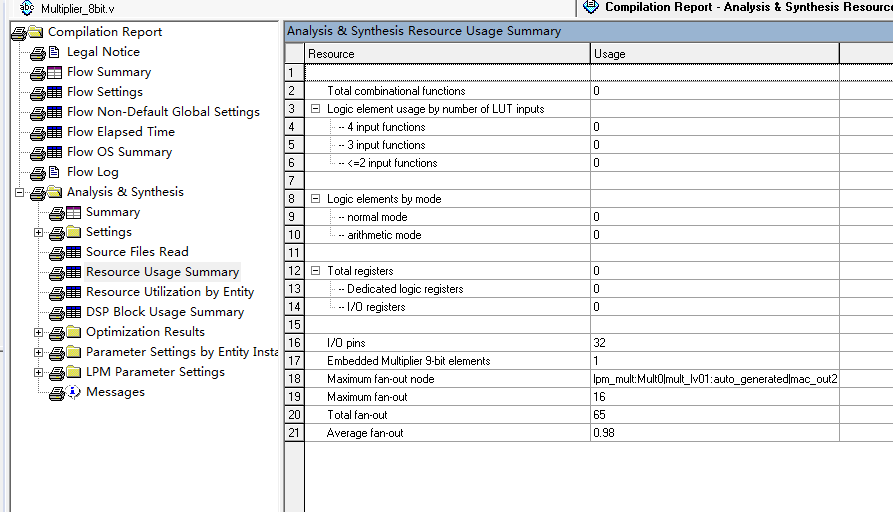

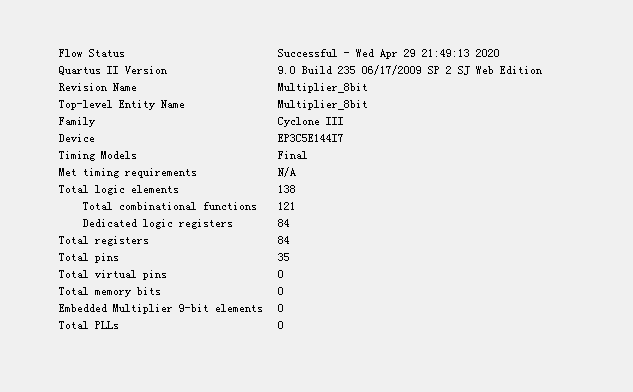

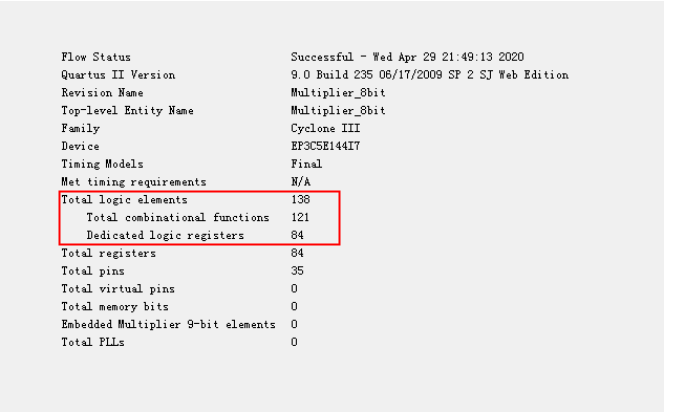

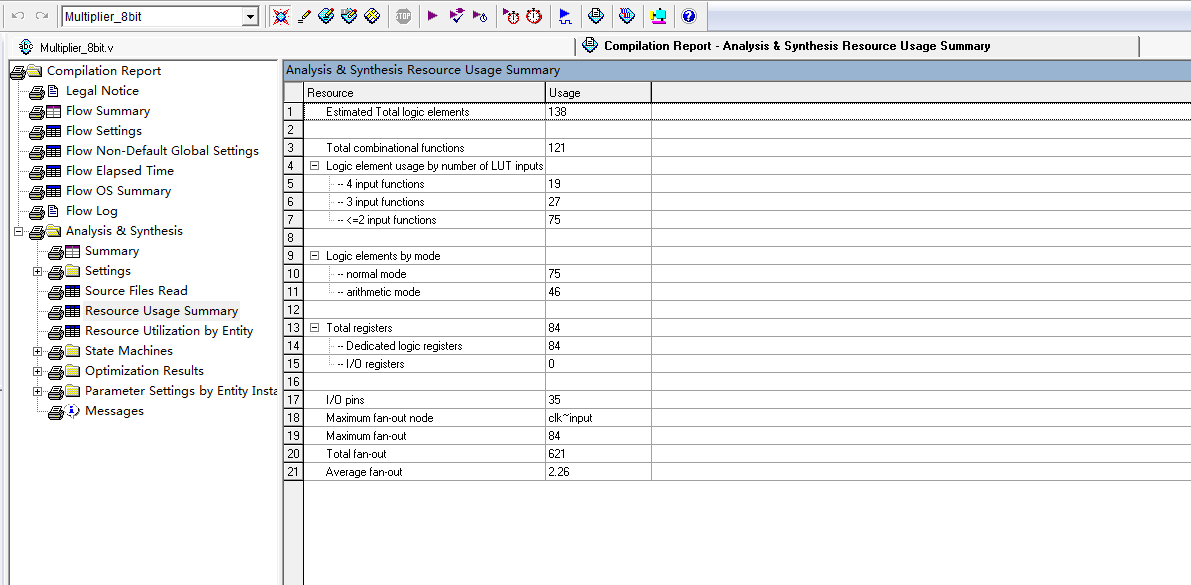

4. 资源占用

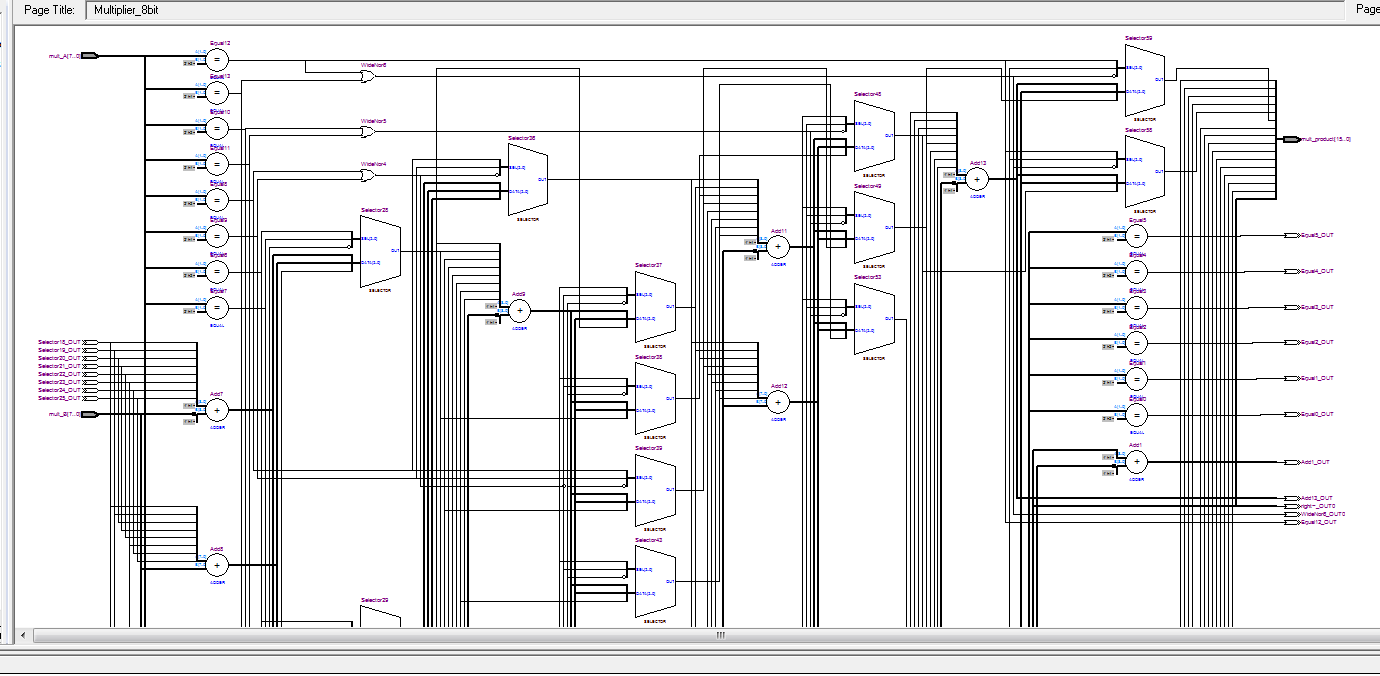

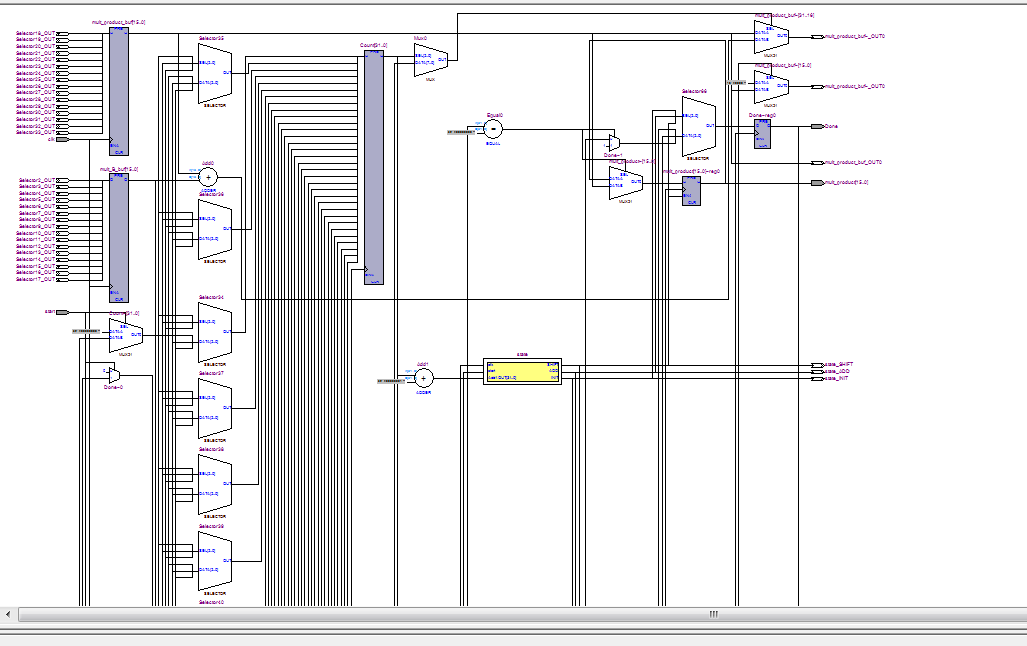

5. RTL图

6. 仿真文件

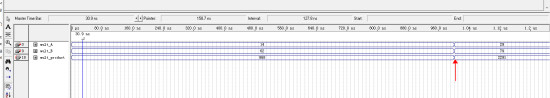

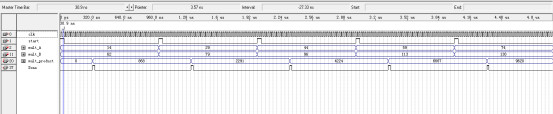

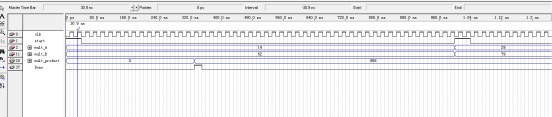

7. 仿真图

1. 工程文件

2. 程序文件

3. 程序编译

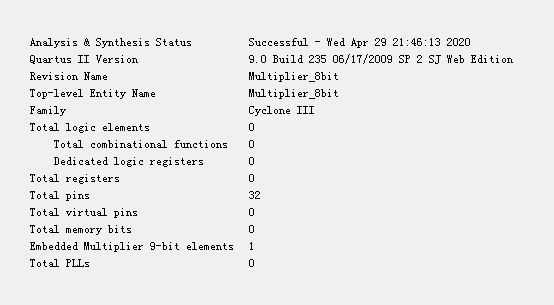

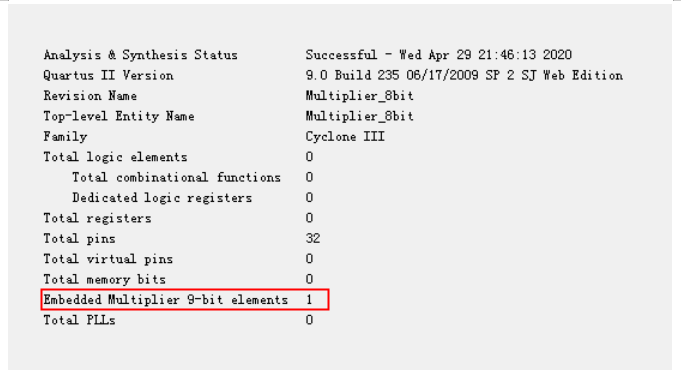

4. 资源占用

占用了内部的专用乘法器资源,没有用逻辑资源

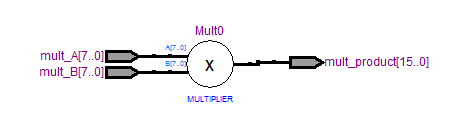

5. RTL图

6. 仿真文件

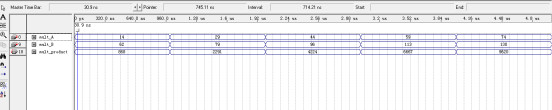

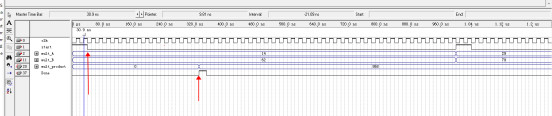

7. 仿真图

可以看到仿真结果直接计算出来,没有延迟

1. 工程文件

2. 程序文件

3. 程序编译

4. 资源占用

5. RTL图

6. 仿真文件

7. 仿真图

部分代码展示:

module Multiplier_8bit(mult_A, mult_B, mult_product);

parameter width=8;

input [width-1:0] mult_A;

input [width-1:0] mult_B;

output [width+width-1:0] mult_product;

reg [width+width-1:0] mult_product;

integer Count;

reg [width+width:0] PA,right;

always @ (mult_A or mult_B)

begin

PA[width+width:0]={16'b0,mult_A,1'b0}; //{mult_product, mult_A, 1'b0}

for(Count=0;Count<width;Count=Count+1)

begin

case(PA[1:0])

2'b10://

begin

//PA=PA-mult_B ;

PA[width+width:width+1]=PA[width+width:width+1] - mult_B[width-1:0];

rightsh1(PA,right);

end

2'b01:

begin

//PA=PA+mult_B

PA[width+width:width+1]=PA[width+width:width+1] + mult_B[width-1:0];

rightsh1(PA,right);

end

源代码

扫描文章末尾的公众号二维码

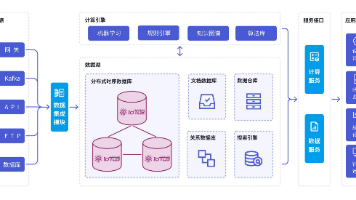

魔乐社区(Modelers.cn) 是一个中立、公益的人工智能社区,提供人工智能工具、模型、数据的托管、展示与应用协同服务,为人工智能开发及爱好者搭建开放的学习交流平台。社区通过理事会方式运作,由全产业链共同建设、共同运营、共同享有,推动国产AI生态繁荣发展。

更多推荐

已为社区贡献37条内容

已为社区贡献37条内容

所有评论(0)