02嵌入式系统硬件环境与软件基础

指令和数据保存在同一内存中,不能同时读指令和读写数据,使用同一个总线系统;指令缓存(instruction cache)和数据缓存(data cache)分开——哈佛结构。当从更远端的存储器读取指令或数据时,就更像是冯罗伊曼结构,指令可以和数据一样移动,并不独立区分。嵌入式DSP处理器 Embedded Digital Signal Processor。拥有不同的代码和数据的地址空间,即使没有缓存

·

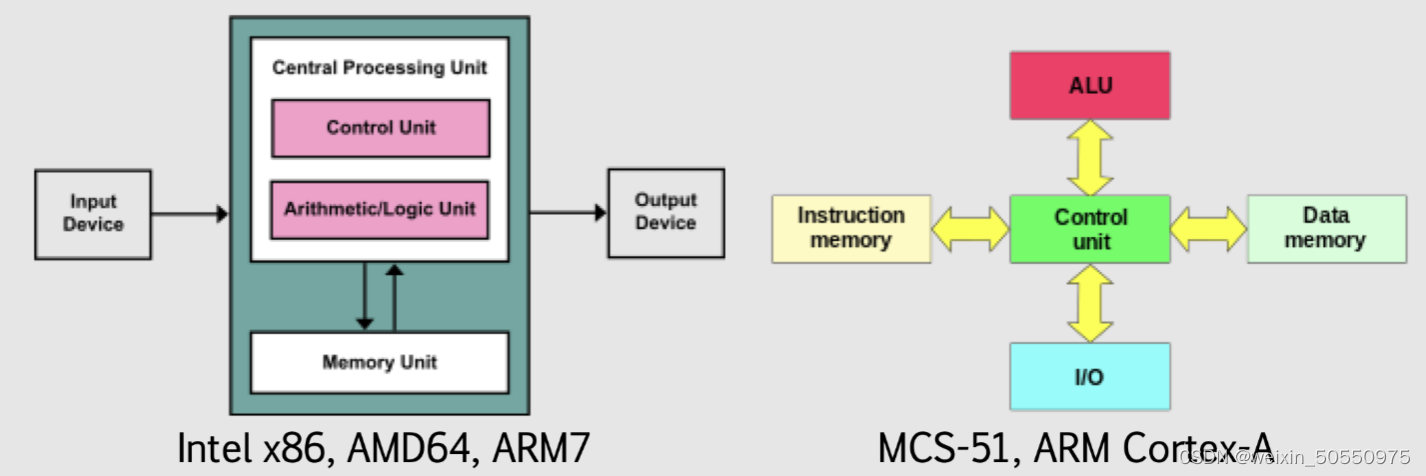

计算机体系架构

冯诺依曼架构

指令和数据保存在同一内存中,不能同时读指令和读写数据,使用同一个总线系统;缓存和流水线结构疏解了瓶颈,再加上分支预测算法

哈佛架构

拥有不同的代码和数据的地址空间,即使没有缓存,也可以同时读取代码和数据

改进的哈佛架构 arm x86

指令缓存(instruction cache)和数据缓存(data cache)分开——哈佛结构

当从更远端的存储器读取指令或数据时,就更像是冯罗伊曼结构,指令可以和数据一样移动,并不独立区分

CPU架构与CPU指令集

架构

- ALU

- 地址寄存器

- 指令解码/ 控制器

- 数据输入输出寄存器

- 寄存器

- 用户/ 通用寄存器

数据存储器

地址存储器

- 控制存储器

程序存储器

执行存储器

- 状态存储器

程序状态寄存器

中断寄存器

指令集

- 精简指令集 RISC,Reduced Instruction Set Computing: 针对流水线化的处理器优化,用更精简的一系列指令来完成使用几率小的同一个任务. 如ARM处理器、MIPS处理器

- 复杂指令集 CISC,Complex Instruction Set Computing: 特点是指令数目多而复杂,每条指令字长并不相等, 如x86处理器、AMD64处理器

处理器两种工作模式

CPU提供硬件支持区分

- 特权模式 (核心态/ 管态, Kernel Mode, privileged mode)

- 普通模式 (用户态/ 常态/ 目态, User Mode)

字节端序

以太网先传高字节,但每字节内先传低有效位

嵌入式处理器的分类和典型微处理器

嵌入式微处理器 Microprocessor

- PowerPC 可伸缩性好, 方便灵活

- MIPS 精简指令集RISC处理器架构

- ARM Advanced RISC Machine

嵌入式微控制器 Microcontroller Unit

嵌入式DSP处理器 Embedded Digital Signal Processor

魔乐社区(Modelers.cn) 是一个中立、公益的人工智能社区,提供人工智能工具、模型、数据的托管、展示与应用协同服务,为人工智能开发及爱好者搭建开放的学习交流平台。社区通过理事会方式运作,由全产业链共同建设、共同运营、共同享有,推动国产AI生态繁荣发展。

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)