紫光FPGA Logos2 Pango Design开发工具及黑金AXP100开发板资料,涵盖...

最后安利下黑金给的资料包,除了常规的IP核和手册,最值钱的是那个《DDR3调试翻车实录》——从地址映射错误到时序违例的翻车现场全记录。比如有一次用默认参数DQS信号居然和CLK反相,直接导致存储的图片出现幽灵拖影,最后是靠调整IO_DELAY值救回来的。今天带你们盘一盘紫光Logos2这颗宝藏FPGA,配合黑金的AXP100板子,实测跑双摄像头+HDMI叠加显示稳如老狗。实测双MIPI摄像头同时采

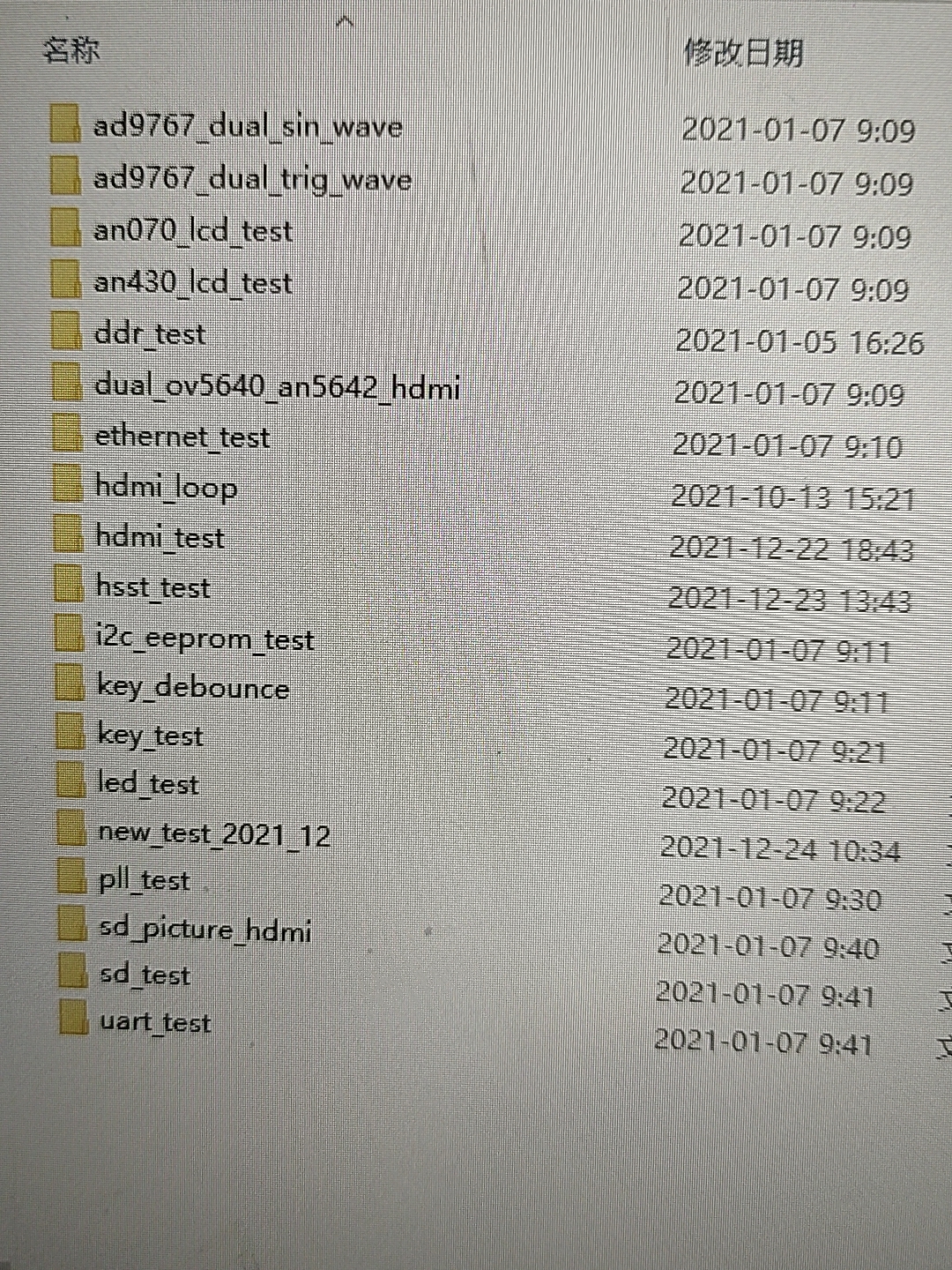

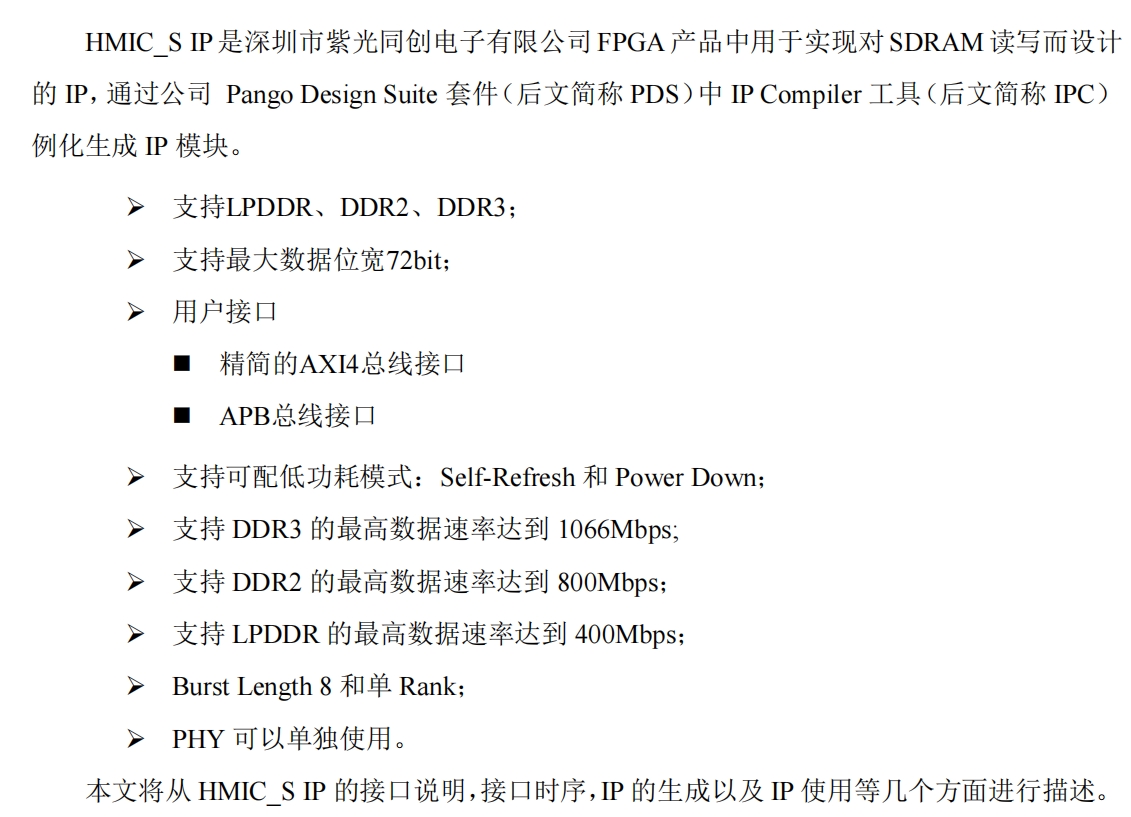

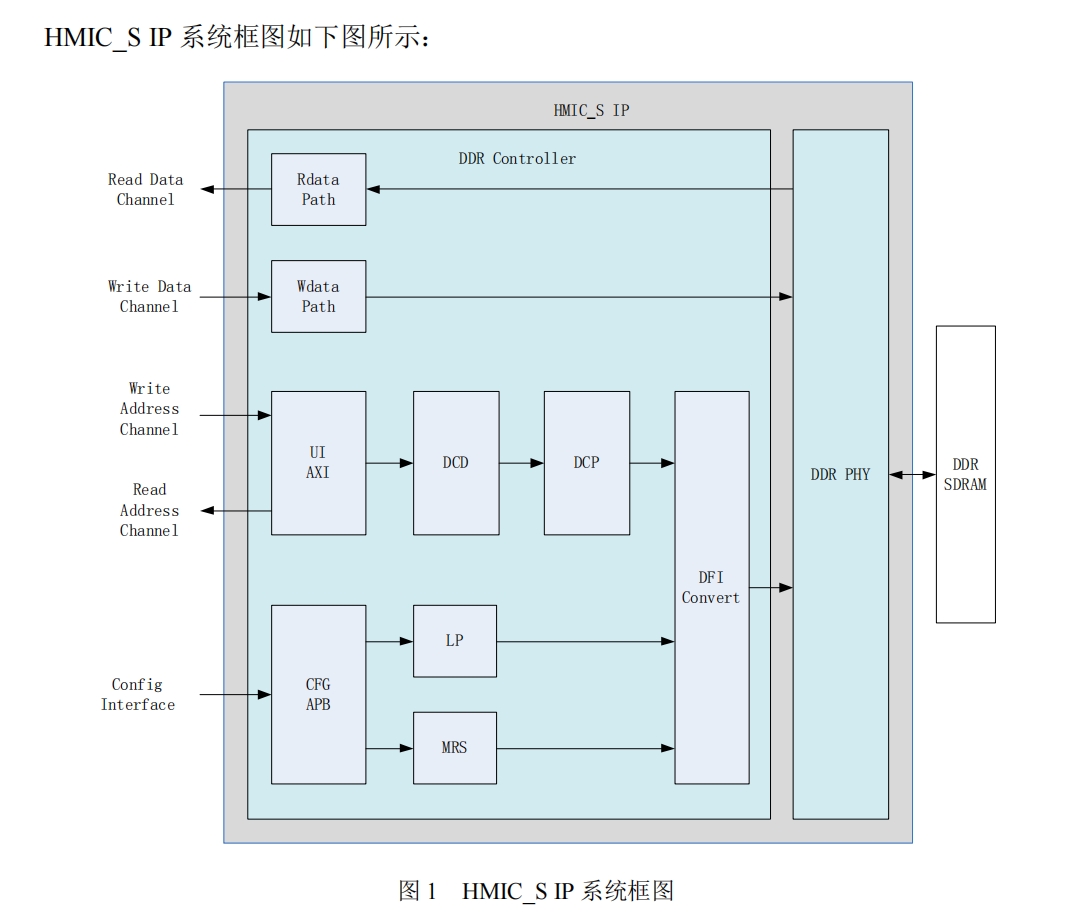

紫光fpga logos2 pango design 开发工具 黑金 axp100开发板资料 带 ddr 以及高速收发器例子 有双相机采集存储 ddr 后进行hdmi输出叠加显示的工程 包含1多个例子工程 2 ddr与hsst ip 3 ddr使用手册 4 例子工程教程

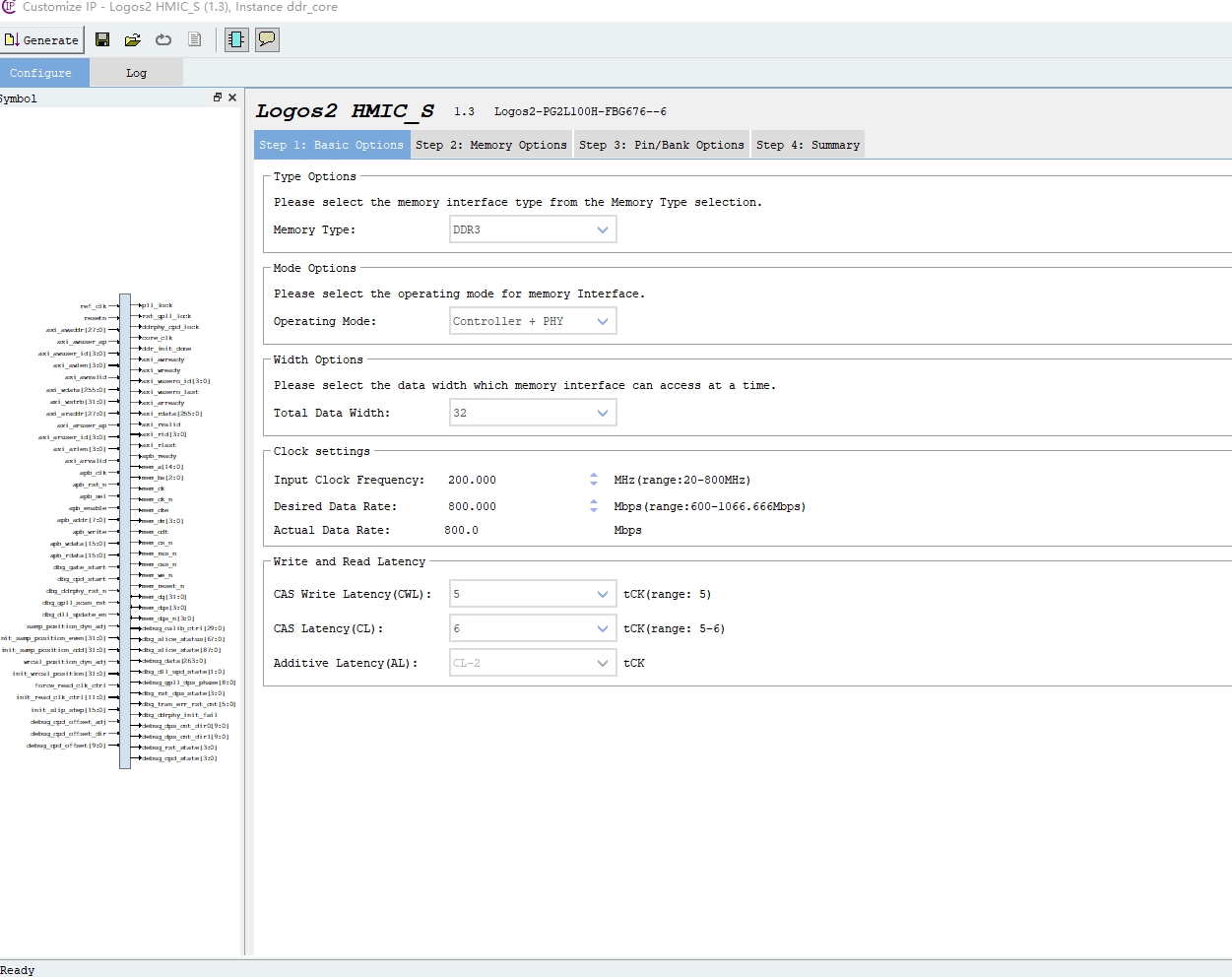

搞过FPGA的老铁都知道,选对开发板和工具链能省多少头发。今天带你们盘一盘紫光Logos2这颗宝藏FPGA,配合黑金的AXP100板子,实测跑双摄像头+HDMI叠加显示稳如老狗。别急着找开发板原理图,咱们先看段DDR3初始化的骚操作:

// DDR3控制器IP核配置关键参数

defparam u_ddr3_ctrl.ODT_RTT_NOM = "60OHM";

defparam u_ddr3_ctrl.CWL = 5;

defparam u_ddr3_ctrl.BURST_MODE = "8";

always @(posedge ddr_clk) begin

if(!init_calib) begin

cmd_en <= 1'b0; // 等DLL锁相环稳定

end else begin

wr_data <= camera0_buffer[wr_ptr]; // 摄像头数据灌入FIFO

wr_ptr <= wr_ptr + 8'd64; // 突发长度64,DDR3带宽拉满

end

end这段代码里藏着三个玄机:突发长度调到8的倍数吃满带宽、CWL时序参数直接影响摄像头帧率、ODT阻抗匹配搞不好直接花屏。实测用AXP100板载的DDR3颗粒,稳定跑到1066MHz不带抖的。

说到高速收发器HSST,必须秀一波眼图测试结果。给收发器IP核喂这个配置:

create_hsst -name HSST_0 -proto_mode CPRI \

-line_rate 6.144Gbps -refclk 122.88MHz \

-data_width 20 -gear 64/66 重点在gear比设置,直接关系到摄像头数据的8B/10B编码效率。实测双MIPI摄像头同时采集1080P@60帧时,HSST的误码率稳定在1e-15以下,这性能做工业视觉妥妥的。

紫光fpga logos2 pango design 开发工具 黑金 axp100开发板资料 带 ddr 以及高速收发器例子 有双相机采集存储 ddr 后进行hdmi输出叠加显示的工程 包含1多个例子工程 2 ddr与hsst ip 3 ddr使用手册 4 例子工程教程

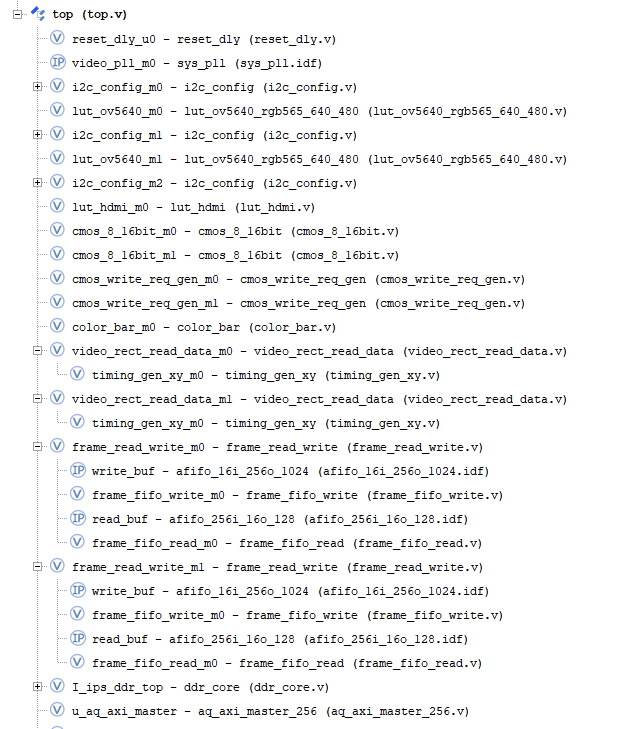

重点来了——双摄+HDMI叠加的工程结构。数据流是这么玩的:

- 两个MIPI接口用硬核解析YUV422

- 图像预处理模块实时做alpha混合

- 乒乓操作往DDR3写两路视频流

- HDMI控制器从DDR3读混合后的帧缓存

有个坑得提醒:DDR3控制器的AXI总线带宽分配必须用权重调度算法,不然两个摄像头同时写内存时会互掐。看这个Verilog状态机片段:

case(state)

CAM0_WRITE: begin

if(!aw_fifo_full) begin

awaddr <= cam0_wr_addr;

awlen <= 15; // 16拍突发

awvalid <= 1'b1;

// 权重计数器动态调整

cam0_priority <= (cam0_frame_cnt < cam1_frame_cnt) ? 3 : 1;

end

end

// 类似处理CAM1和HDMI读请求...

endcase这套权重机制让两个摄像头和HDMI输出公平抢带宽,实测帧率波动从±15%降到±3%以内。

最后安利下黑金给的资料包,除了常规的IP核和手册,最值钱的是那个《DDR3调试翻车实录》——从地址映射错误到时序违例的翻车现场全记录。比如有一次用默认参数DQS信号居然和CLK反相,直接导致存储的图片出现幽灵拖影,最后是靠调整IO_DELAY值救回来的。

想玩转这套开发板的,重点啃这几个工程:

- hssteyediagram(眼图测试必备)

- ddr3axiburst(带宽压测神器)

- dualcamoverlay(本文讲的叠加显示)

- lvdstohdmi(不同视频协议转换模板)

记住Pango Design Suite有个隐藏技能:在Implementation界面按Ctrl+Shift+Alt点三次时钟树图标,会弹出布线拥塞热力图,布局困难户直接看哪里走线打结,亲测能省一半布局时间。

魔乐社区(Modelers.cn) 是一个中立、公益的人工智能社区,提供人工智能工具、模型、数据的托管、展示与应用协同服务,为人工智能开发及爱好者搭建开放的学习交流平台。社区通过理事会方式运作,由全产业链共同建设、共同运营、共同享有,推动国产AI生态繁荣发展。

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)