芯片lot与wafer的关系

是一片薄薄的、圆形的硅片,是制造芯片的。

Lot(批) 和 Wafer(晶圆) 是半导体工厂中生产管理和追溯的两个基本单位,它们之间是典型的 包含与被包含 的关系。

我们可以用一个生动的比喻来理解:

-

一个Lot(批) 就像 “一个年级的所有班级”。

-

一片Wafer(晶圆) 就像 “年级中的一个班级”。

-

一个Die(芯片) 就像 “班级里的一个学生”。

一、 核心定义

1. Wafer - 晶圆

-

是什么:是一片薄薄的、圆形的硅片,是制造芯片的 “地基”。通过一系列复杂的前道工艺(光刻、刻蚀、离子注入、薄膜沉积等),在一片晶圆上可以同时制造出成百上千个独立的 芯片。

-

关键属性:

-

尺寸:常见的如8英寸(200mm)、12英寸(300mm)。尺寸越大,单次能生产的芯片数量越多,成本效益越高。

-

工艺节点:指制造技术水平,如28nm、7nm、5nm等。

-

Wafer ID:每一片晶圆都有一个唯一的条形码或二维码,用于全程追溯。

-

2. Lot - 批

-

是什么:是半导体制造和运输的 基本管理单位。一个Lot包含 一组(通常是25片) 被 一起处理 的晶圆。

-

关键属性:

-

Lot ID:每一个批都有一个唯一的编号,这是整个生产流程中最核心的追溯码。

-

标准化:使用标准数量的晶圆(如25片)是为了适配标准的 FOUP 的容量,从而实现自动化搬运和加工。

-

二、 Lot和Wafer的层级关系

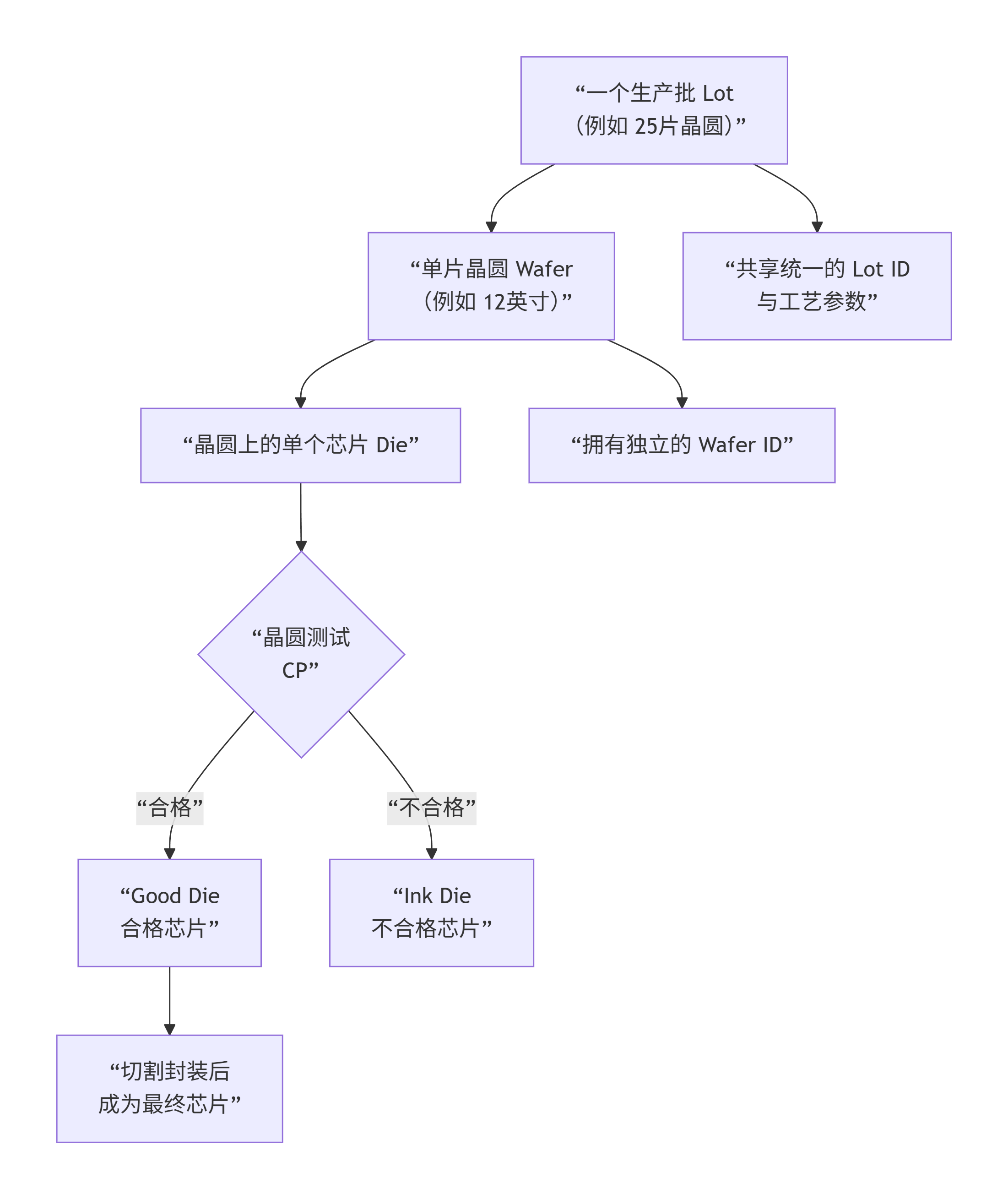

下图清晰地展示了从Lot到最终芯片的完整层级关系与流程:

解读与详解:

-

从Lot到Wafer:

-

一个 Lot 就像一个 “生产任务包”。晶圆厂收到一个订单,不会一片一片地加工晶圆,而是以一个Lot为单位进行调度和生产。

-

这25片(举例)晶圆会被放入一个 FOUP 中,然后由自动化物料搬运系统将它们 作为一个整体,运送到不同的加工设备(如光刻机、刻蚀机)进行处理。

-

为什么这么做?

-

效率:一次性处理多片晶圆,最大化设备利用率。

-

一致性:确保同一个Lot内的所有晶圆经历完全相同的工艺条件(温度、压力、化学试剂浓度、时间等),以保证芯片性能的一致性和稳定性。

-

可追溯性:通过Lot ID,可以精确追溯这组晶圆在任何时间点、在哪台设备上、由哪个工程师操作、使用了哪些工艺配方和物料。

-

-

-

从Wafer到Die:

-

每一片 Wafer 上,都通过前道工艺制作出了大量的独立功能单元,这些单元被称为 Die。

-

在Wafer制造完成后,会进行 晶圆测试,用探针测试每个Die的电性参数和功能。合格的Die会被标记为 Good Die,不合格的则会被点上墨点标记为 Ink Die,在后续封装环节中被舍弃。

-

良率:一片Wafer上 Good Die的数量 / 总Die的数量 就是该片Wafer的良率。

-

三、 生产流程中的Lot与Wafer

-

起点:一批空白硅片被赋予一个 Lot ID,开始它们的旅程。

-

加工:这个Lot被整体运送到各个工艺区域。虽然是一起处理,但设备通常会 一片接一片地 对Lot中的Wafer进行加工。

-

数据监控:在生产过程中,会对Lot中的 每一片Wafer 进行抽样测量。如果发现某片Wafer的关键参数异常,工程师可以及时调整工艺,防止整个Lot报废,从而节约成本。

-

测试与分选:工艺完成后,整个Lot被送到测试区,对 每一片Wafer 上的 每一个Die 进行测试。

-

结束:测试完成后,Wafer被切割。Good Die被送去封装,而整个Lot的生产数据(包括每片Wafer的良率和每个Die的性能)都被记录在数据库中,关联着 Lot ID 和 Wafer ID。

四、 总结与类比

| 概念 | 比喻 | 关系与作用 | 标识 |

|---|---|---|---|

| Lot(批) | 一个年级 | 生产管理的基本单位,保证组内晶圆加工的一致性,便于调度和追溯。 | Lot ID |

| Wafer(晶圆) | 一个班级 | 芯片的载体和制造单位,是工艺加工和测试的直接对象。 | Wafer ID |

| Die(芯片) | 一个学生 | 最终的产品个体,是功能和价值的体现。 | 在Wafer上的坐标 |

核心关系总结:

-

一个Lot包含多片Wafer。

-

一片Wafer包含多个Die。

-

Lot级管理 关注的是 宏观的生产效率、一致性和流程控制。

-

Wafer级和Die级 关注的是 微观的个体性能、缺陷控制和最终良率。

理解Lot和Wafer的关系,是理解半导体制造、质量控制和成本分析的基础。它体现了半导体工业如何通过精密的系统化管理和自动化技术,来实现大规模、高效率、高复杂度的芯片生产。

五、 Lot管理的核心目标

在深入技术细节前,首先要明白为什么要如此严格地管理Lot:

-

全程可追溯性:任何一颗芯片,都能通过其Lot ID追溯到他出生、成长的所有环境、经历和“体检报告”。

-

保证一致性:确保同一个Lot内的所有晶圆经历完全相同的工艺条件,产出性能一致的芯片。

-

最大化良率:实时监控,快速定位并隔离问题,防止缺陷扩散,提升整体良率。

-

优化生产效率:实现自动化调度,减少设备等待时间,提升工厂产能。

六、同一个Lot内的Wafer,其良率通常非常接近,但几乎不可能完全相同。

追求良率一致是半导体制造的核心目标,但现实中存在诸多因素导致细微差异。下面我们详细拆解为何会如此。

理想情况:为什么我们希望它们相同?

在一个完美的世界里,同一个Lot的所有Wafer应该具有完全相同的良率。因为它们是作为一个整体被管理的:

-

相同的原材料:来自同一批次的空白硅片。

-

相同的工艺配方:使用相同的化学试剂、气体、工艺参数(温度、压力、时间等)。

-

相同的设备与环境:在同一个FOUP中,依次通过同一台设备,在相同的洁净室环境中加工。

-

相同的时间窗口:所有加工步骤在很短的时间间隔内完成。

这种高度一致的处理方式,旨在将所有Wafer的初始条件和加工经历之间的差异降到最低。因此,它们的良率会聚集在一个非常狭窄、可预测的范围内。

为啥会有差异呢?

1. 晶圆自身的固有差异

-

即使来自同一晶棒,不同位置的硅片在晶格缺陷、掺杂均匀性、平坦度等方面也存在纳米级别的微小差异。这些“先天”的不同,会直接影响后续工艺的结果。

2. 工艺处理中的“队列效应”

-

虽然一个Lot的Wafer在同一个设备上加工,但它们是一片接一片地进入工艺腔体的,而不是25片同时进去。

-

举例:

-

第一片 vs. 最后一片:在化学气相沉积中,第一片晶圆进入时,腔体壁和气体环境是“干净”的。当最后一片进入时,腔体壁可能已经沉积了少许前序工艺的副产物,或者气体比例有极其微小的漂移,这可能导致薄膜厚度有 angstrom 级别的差异。

-

设备预热/稳定:设备在长时间运行后,其温度、等离子体状态可能比刚开始时更稳定。

-

3. 设备内部的“腔体效应”

-

对于拥有多个工艺腔体的集群设备,不同腔体之间可能存在无法完全消除的微小差异(如气流分布、电极平整度)。

-

虽然先进工艺控制会尽力匹配各腔体性能,但绝对的同一性是无法实现的。一个Lot的Wafer可能被分配到不同的腔体进行处理,从而引入差异。

4. 随机缺陷

-

这是导致良率差异最主要、最不可预测的因素。

-

来源:微小的尘埃颗粒、设备部件的瞬间异常、化学试剂的微小杂质等。

-

影响:这些随机事件就像“中彩票”,可能击中任何一片Wafer上的任何一颗Die。一片Wafer可能幸运地躲过了大部分随机缺陷,而另一片则可能被击中多次。 这是导致良率波动的主要原因。

5. 量测与测试的统计误差

-

晶圆测试本身也存在极低的误判率。一个本该是好的Die可能被误判为坏,反之亦然。这种测试噪声也会贡献微小的良率差异。

魔乐社区(Modelers.cn) 是一个中立、公益的人工智能社区,提供人工智能工具、模型、数据的托管、展示与应用协同服务,为人工智能开发及爱好者搭建开放的学习交流平台。社区通过理事会方式运作,由全产业链共同建设、共同运营、共同享有,推动国产AI生态繁荣发展。

更多推荐

已为社区贡献6条内容

已为社区贡献6条内容

所有评论(0)