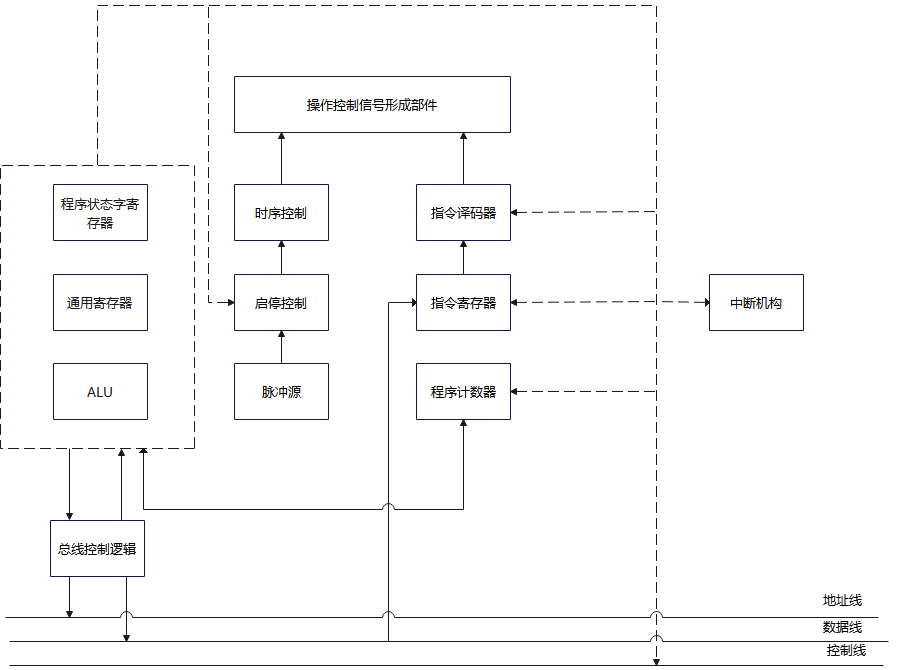

计算机组成原理——CPU介绍

组合逻辑元件的输出仅由当前输入决定,例如加法器、多路选择器等,只要输入信号发生变化,输出就会立即随之改变(考虑门延迟)。现代CPU采用预取技术,PC实际指向的是正在预取的指令地址,通过指令流水线实现并行执行。它通过**选择信号(Select)**控制输出路径,例如在32位系统中,当Select=0时输出A通道的数据,Select=1时输出B通道的数据。32位加法器由多个1位全加器级联构成,输入包括

一.CPU控制原理

1. 总线控制逻辑

总线控制逻辑是CPU与地址/数据/控制总线交互的核心枢纽,负责协调数据传输的时序和路径。它通过锁存复用信号(如8086的AD15-AD0地址/数据复用线)确保地址信息在T1周期被稳定锁存,后续周期用于数据传输。在最大模式下,总线控制器(如8288)根据CPU状态信号(S2-S0)生成存储器读写命令,实现多处理器系统的协同。其关键功能包括总线仲裁(集中式或分布式)和信号分离,避免冲突并提高并行性。

2. 脉冲源和启停控制

脉冲源通常由石英晶体振荡器生成基准时钟信号(如8086的CLK),占空比33%为最优,频率5-10MHz。启停逻辑通过触发器(如运行标志C1)控制时钟信号的传递:当C1=1时允许脉冲通过,启动CPU操作;C1=0时冻结时序,暂停处理。这一机制确保计算机各部件严格按时钟节拍同步工作,是时序系统的基础。

3. 时序控制

时序控制以时钟脉冲为基准,将指令周期划分为机器周期、节拍和工作脉冲三级。例如,8086的基本总线周期包含T1-T4四个状态,T1发送地址,T2-T4传输数据。同步控制方式下,所有操作按最长指令时间统一节拍;异步方式则通过应答信号(如WAIT)动态调整时序。微程序控制器简化了时序逻辑,仅需节拍-脉冲二级体制。

4. 程序计数器(PC)

PC存储下一条待执行指令的地址,初始值由复位信号(RESET)设为0FFFFH。取指阶段,PC内容送MAR并自动+1(或加载跳转地址);中断时,PC当前值压栈保护,确保返回后继续执行。PC的位数决定寻址范围(如32位PC可寻址4GB空间),且多线程环境下各线程拥有独立PC。

5. 指令寄存器(IR)

IR暂存从存储器取出的当前指令,其输出分为操作码(送ID译码)和地址码(送地址形成部件)。例如,在x86架构中,IR接收的指令可能包含前缀、操作码和ModR/M字节,由控制单元解析后生成微操作序列。IR的位数与指令字长一致(如RISC-V的32位固定长度)。

6. 指令译码器(ID)

ID将IR中的操作码转换为控制信号。例如,ADD指令经译码后,ID会激活ALU的加法电路并选择输入寄存器。硬布线控制器中,ID输出直接驱动组合逻辑;微程序控制器中,ID生成微程序入口地址,从控制存储器读取微指令。ID的设计直接影响指令集兼容性和执行效率。

7. 中断机构

中断机构处理异常和外部请求,通过IRQ线接收信号(如键盘输入触发IRQ1)。CPU响应中断时,保存PSW和PC到栈中,跳转至中断向量表指定入口(如x86的INT 0x80调用系统服务)。中断优先级由中断控制器(如8259A)管理,支持嵌套和屏蔽。现代CPU还引入虚拟中断(VIF/VIP)支持虚拟化。

8. 操作控制信号产生部件

该部件综合时序信号(节拍)、译码结果(ID输出)和状态(PSW标志位)生成微操作序列。例如,在取指周期,它发出PC→MAR、1→R等信号;执行阶段则根据指令类型控制ALU或I/O操作。硬布线控制器通过组合逻辑实现,延迟低但修改困难;微程序控制器则依赖查表,灵活性高。

以上部件协同工作,构成计算机控制器的完整框架。

二.数据通路

组合逻辑元件和状态元件是数字电路的两大基础类型,它们在功能特性上存在本质区别。组合逻辑元件的输出仅由当前输入决定,例如加法器、多路选择器等,只要输入信号发生变化,输出就会立即随之改变(考虑门延迟)。这类元件没有记忆功能,适用于即时数据处理和逻辑运算。状态元件则具有存储能力,其输出不仅取决于当前输入,还依赖于电路的历史状态,典型代表包括触发器、寄存器等。

从电路结构来看,组合逻辑通常由基本逻辑门(如与门、或门)直接连接而成,不包含反馈回路。状态元件则包含存储单元和反馈路径,通过时钟信号控制状态的更新。例如,D触发器在时钟上升沿将输入数据锁存并保持,直到下一个时钟周期才会更新。这种结构差异使得状态元件能够实现信息的存储和时序控制。

在实际应用中,组合逻辑负责即时数据处理,如算术运算、信号选择等;状态元件则用于需要记忆功能的场合,如状态机、计数器、寄存器等。两者通常协同工作:组合逻辑处理数据流,状态元件保存中间结果,共同构成完整的数字系统。这种分工配合使得计算机既能进行快速运算,又能保持稳定的系统状态。

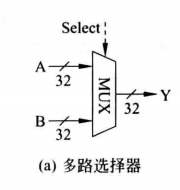

1. 多路选择器(MUX)

多路选择器(MUX)是一种数据选择电路,用于从多个输入信号中选择一个输出。它通过**选择信号(Select)**控制输出路径,例如在32位系统中,当Select=0时输出A通道的数据,Select=1时输出B通道的数据。MUX广泛应用于计算机的数据通路,如寄存器文件的数据选择、总线切换等,确保正确的数据流向目标部件。

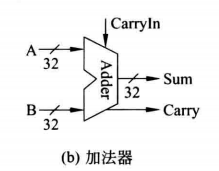

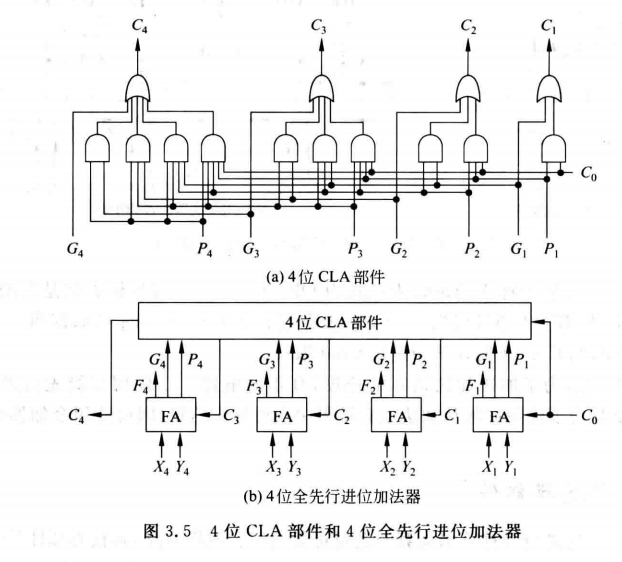

2. 加法器(Adder)

加法器是计算机算术运算的核心部件,用于执行二进制加法。32位加法器由多个1位全加器级联构成,输入包括两个32位操作数(A、B)和一个进位(CarryIn),输出32位和(Sum)及进位(CarryOut)。加法器不仅用于算术运算,还可通过补码转换实现减法,并用于地址计算(如PC+4)。

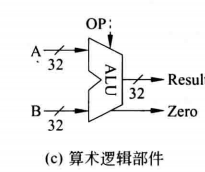

3. 算术逻辑部件(ALU)

ALU(算术逻辑单元)是CPU的核心运算部件,负责执行算术(加、减)、逻辑(与、或、非、异或)和比较运算。它通过OP码选择运算类型,并输出结果及状态标志(如Zero标志用于判断是否相等)。32位ALU可在一个时钟周期内完成运算,是计算机执行指令的关键组件。

4. 译码器(Decoder)

译码器用于将编码输入转换为对应的控制信号,如3-8译码器可将3位二进制输入(000~111)转换为8个输出信号(每次仅一个有效)。在计算机中,译码器用于指令解码(解析操作码)、存储体选择(如选择RAM或ROM)以及外设控制(如片选信号)。它确保控制信号能准确作用于目标设备。

三.数据总线

1.寄存器

一、用户可见寄存器组

-

程序计数器(PC) PC是CPU中的地址指针寄存器,其核心功能是指向下一条待执行指令的内存位置。工作原理是:当CPU执行完当前指令后,PC会自动增加一个指令长度(通常为1-15字节),指向下一条指令;遇到跳转指令时,PC直接加载目标地址;中断发生时,当前PC值会被压入堆栈保存。现代CPU采用预取技术,PC实际指向的是正在预取的指令地址,通过指令流水线实现并行执行。

-

程序状态字(PSW) PSW是反映和控制CPU运行状态的多功能寄存器。其工作原理是通过多个状态位记录运算结果特征:零标志位(ZF)表示结果是否为0,进位标志(CF)记录无符号数溢出,溢出标志(OF)检测有符号数溢出。控制位包括中断使能位(IF)控制中断响应,陷阱标志(TF)用于单步调试。这些标志位由ALU自动设置,并影响后续条件跳转指令的执行流程。

-

通用寄存器组 通用寄存器是CPU内部的高速数据存储单元,采用多端口SRAM结构实现。工作原理是:在执行指令时,寄存器文件根据地址解码结果同时读取2-3个操作数,并将结果写回指定寄存器。现代CPU采用寄存器重命名技术,将架构寄存器映射到更大的物理寄存器文件,解决数据冒险问题。寄存器窗口技术通过动态分配寄存器组来优化函数调用开销。

-

累加器(ACC) 累加器是专用于算术运算的寄存器,其工作原理是作为ALU的默认操作数。在乘法指令中自动存储乘积低半部分,除法指令中存储商。现代CPU虽将其融入通用寄存器体系,但仍保留特殊用途:x86架构中AX寄存器在IO操作时自动与设备寄存器交互,MIPS架构中HI/LO寄存器专用于乘除结果存储。

二、汇编程序可见寄存器

-

中断字寄存器 中断字寄存器通过位向量控制中断系统。其工作原理是:每个中断源对应一个控制位,置1表示允许中断。优先级编码器选择最高优先级的中断请求,中断屏蔽寄存器可动态屏蔽特定中断。现代CPU采用分层中断控制,硬件自动保存被中断程序的PSW和PC,并加载中断服务例程的入口地址。

-

基址寄存器 基址寄存器实现动态地址重定位。其工作原理是:CPU产生的逻辑地址与基址寄存器内容相加生成物理地址。现代系统使用多组基址寄存器实现分段存储管理,MMU配合页表完成虚拟地址转换。专用界限寄存器防止越界访问,实现存储保护。

-

变址寄存器 变址寄存器支持复杂寻址模式。其工作过程是:指令指定基址寄存器、变址寄存器和比例因子(1/2/4/8),ALU计算有效地址=基址+变址×比例。这种机制特别适合处理数组和结构体,循环中只需递增变址寄存器即可遍历数据。现代CPU配备专用地址生成单元(AGU)并行计算多个内存地址。

-

条件码寄存器 条件码寄存器是PSW的运算结果子集。其工作过程是:ALU执行运算后自动设置标志位,条件跳转指令(Jcc)测试这些标志决定分支。超标量CPU采用条件码转发技术,将标志位提前传递给分支预测单元,减少流水线停顿。ARM架构允许大多数指令选择性更新条件码。

三、用户不可见寄存器

-

内存地址寄存器(MAR) MAR是CPU与内存的地址接口寄存器。其工作流程是:在取指周期存储PC值,在访存周期存储ALU计算的地址。现代CPU采用虚拟MAR,经TLB转换后生成物理地址。多级流水线中设置多个MAR副本,支持同时进行指令预取和数据访问。

-

内存数据寄存器(MDR) MDR是数据缓冲寄存器。其工作原理是:读操作时暂存从内存读取的数据,写操作时保持待写入数据直至总线空闲。现代MDR集成ECC校验模块,通过汉明码检测和纠正单比特错误。缓存子系统中MDR设计为缓存行大小,支持突发传输模式。

-

指令寄存器(IR) IR保存当前译码指令。其工作过程是:取指单元将指令存入IR,译码器解析操作码和操作数字段。复杂指令集采用微码机制,将IR内容作为微程序入口地址。超标量CPU设置多个IR实现并行译码,x86架构使用预译码队列将变长指令转为定长微操作。

-

微指令寄存器组 微程序控制器的核心寄存器包括:uIR存储当前微指令,其字段控制数据通路;uMAR指向下条微指令地址,支持条件跳转;uMDR暂存微程序数据。现代CPU采用可重写控制存储器,通过更新uIR内容实现微码补丁,修复处理器设计缺陷。

-

高速缓存(Cache) Cache是SRAM构成的存储层次。其工作原理是:地址分解为标记、索引和偏移三部分,相联查找确定命中。缓存行包含有效位、脏位和替换控制位。具体看我之前写的

魔乐社区(Modelers.cn) 是一个中立、公益的人工智能社区,提供人工智能工具、模型、数据的托管、展示与应用协同服务,为人工智能开发及爱好者搭建开放的学习交流平台。社区通过理事会方式运作,由全产业链共同建设、共同运营、共同享有,推动国产AI生态繁荣发展。

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)