CJC1808芯片采样率为何设置48kHZ??

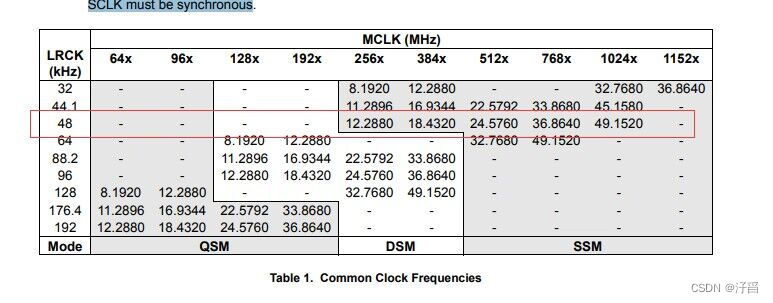

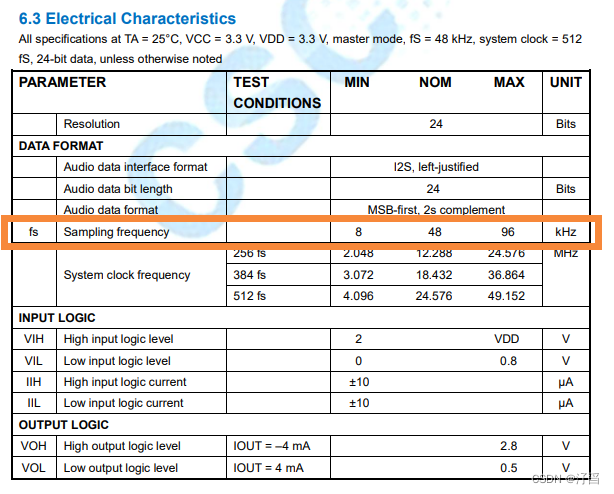

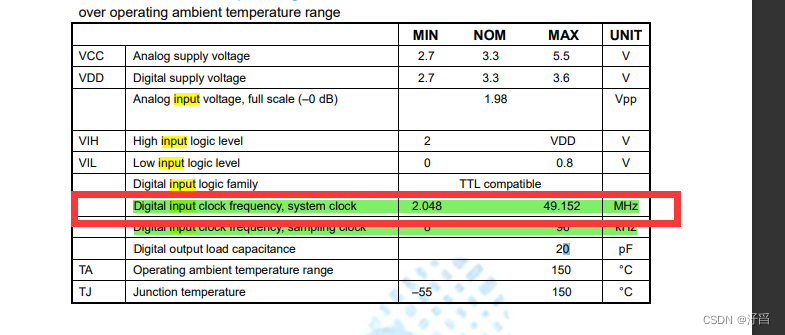

在单个LRCK周期内通过检测MCLK的绝对速度进行转换。表1显示了几种标准音频采样率和所需的MCLK 和 LRCK 频率。请注意,没有必需的相位关系,但MCLK,LRCK和SCLK 必须是同步的.MCLK/LRCK 必须是整数比率,如表 1 所示。LRCK 频率等于 Fs,即每个通道的字输入到设备的频率。MCLK 与 LRCK 的频率比和在初始化序列期间通过计算MCLK的数量自动检测速度模式。为何

MCLK/LRCK must be an integer ratio, as shown in Table 1. The LRCK frequency is equal to Fs, the frequency at which words for each channel are input to the device. The MCLK-to-LRCK frequency ratio and speed mode is detected automatically during the initialization sequence by counting the number of MCLK transitions during a single LRCK period and by detecting the absolute speed of MCLK. Internal dividers are set to generate the proper clocks. Table 1 illustrates several standard audio sample rates and the required MCLK and LRCK frequencies. Please note there is no required phase relationship, but MCLK, LRCK and SCLK must be synchronous.

MCLK/LRCK 必须是整数比率,如表 1 所示。LRCK 频率等于 Fs,即每个通道的字输入到设备的频率。MCLK 与 LRCK 的频率比和在初始化序列期间通过计算MCLK的数量自动检测速度模式

在单个LRCK周期内通过检测MCLK的绝对速度进行转换。内部分隔器是设置为生成正确的时钟。表1显示了几种标准音频采样率和所需的MCLK 和 LRCK 频率。请注意,没有必需的相位关系,但MCLK,LRCK和SCLK 必须是同步的.

为何采样频率不设置为44.1KHZ,是由标准音频采样率和所需的MCLK 和 LRCK 频率所决定的。

魔乐社区(Modelers.cn) 是一个中立、公益的人工智能社区,提供人工智能工具、模型、数据的托管、展示与应用协同服务,为人工智能开发及爱好者搭建开放的学习交流平台。社区通过理事会方式运作,由全产业链共同建设、共同运营、共同享有,推动国产AI生态繁荣发展。

更多推荐

已为社区贡献2条内容

已为社区贡献2条内容

所有评论(0)