如何进行硅后测试

【代码】如何进行硅后测试。

·

1.be simple and fast.

dont use a reference model

而是生成测试用例,并尽量保证覆盖率

2.handler of interrupt

instead of placing the branch instruction into the test stream,

it writes an illegal instruction form.

This way,when the test-case is executed,

the illegal instruction causes an illegal instruction interrupt.

The handler of this interrupt calls a generation function

dedicated to the completion of the branch instruction generation

3.data path selection

22 types of fp number forms -

10 single forms and 12 double forms

normalized,

denormalized,

infinity

We defined a coverage model

that includes the occurrence of all the legal number forms

in the input and outputs operands of the 10 fp instructions.

This model includes 280 different legal events

3.how to checking

execute each generated test-case several times (passes).

After each pass we check that certain resources,

including registers and memory areas,

are consistent and have the same end-of-test values.

In this way, we have the first pass essentially

serve as a reference model.

This consistency is guaranteed by restricting the test-case generation as follows.

First, we do not randomly generate any instruction whose behavior is not fully predictable

This includes, for instance, the Load-and-reserve instruction,

This attempt may succeed or fail depending on run-time conditions

that involve other threads in the system,

and cannot, in general, be predicted during test-case generation

Second, we forbid any write-write collisions on checked memory areas

since we can not predict the order between the colliding write accesses.

Third, we must ensure that any data written to a checked resource is deterministic,

in the sense that it has the same value in every pass

This is achieved either by having another checked resource

serve as the source of the data

or by simply using a constant

4.why use multi-pass consistency checking

Some variability is created automatically,

for example due to page tables filling up and different cache states

the ordering of instructions executing in the pipeline of the same thread

can also be different

However, some type of bugs cannot be detected.

For example, a bug in the processor’s datapath causing 1+1=3 will go undetected

referenced:

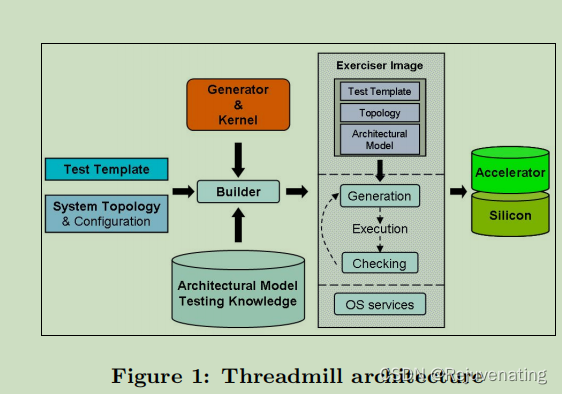

Threadmill: A Post-Silicon Exerciser for Multi-Threaded Processors

魔乐社区(Modelers.cn) 是一个中立、公益的人工智能社区,提供人工智能工具、模型、数据的托管、展示与应用协同服务,为人工智能开发及爱好者搭建开放的学习交流平台。社区通过理事会方式运作,由全产业链共同建设、共同运营、共同享有,推动国产AI生态繁荣发展。

更多推荐

已为社区贡献9条内容

已为社区贡献9条内容

所有评论(0)