版图工程师如何为芯片筑起 ESD 防线

芯片版图工程师如何为芯片筑起ESD防护屏障?静电放电(ESD)对芯片构成致命威胁,可能导致瞬间击穿或潜在损伤。版图工程师通过五大核心准则构建防护体系:均衡分流避免电流拥堵、优化布线降低寄生效应、严守ESD设计规则、功能分区隔离保护、仿真验证查漏补缺。他们需在性能、面积与可靠性间取得平衡,将电路设计转化为可制造的物理结构。随着工艺进步,版图工程师已成为芯片可靠性的关键守护者,其精妙的版图设计决定着芯

一颗拇指盖大小的芯片,浓缩着上百亿晶体管的精密排布,却可能在你不经意的一次触碰中瞬间损毁。在芯片设计的浩瀚版图中,谁在为这份脆弱筑起坚固防线?答案,藏在版图工程师的笔尖与匠心之中。

谈及芯片设计,我们总热衷于探讨架构的精妙、算法的高效、性能的突破 —— 这些堪称芯片的 “大脑” 与 “灵魂”。但一颗芯片能否在真实世界中站稳脚跟、长久服役,却离不开一个看似处于后端,实则贯穿始终的关键环节:物理版图设计。而版图工程师与静电放电(ESD)防护的博弈,正是决定芯片 “体质” 强弱的核心所在。

在微米乃至纳米级的微观战场上,版图工程师如何掂量 ESD 的千钧重量,以精准布局抵御无形威胁?今天,我们一同潜入芯片的微观世界,解锁这场无声守护的密码。

一、无形的利刃:为何 ESD 是芯片的 “劲敌”?

要理解版图工程师的使命,必须正视 ESD 的致命破坏力。

静电放电(ESD),本质是带静电的物体(如人体、设备)通过直接接触或电场感应,向芯片瞬间转移静电荷的过程。这一瞬间短至纳秒到微秒级,电压却能飙升至数千甚至上万伏 —— 足以击穿芯片内部最精密的结构。

人体静电释放击穿芯片内部结构

这种瞬时能量冲击,对芯片的损伤分为两类,无论哪一种都足以致命——

灾难性失效:巨大能量直接熔断金属连线、击穿栅氧层,让芯片功能永久丧失,堪称 “一击致命”。某新能源车企早期 BMS 模块(电池管理系统),就因电源轨未与 ESD 泄放路径隔离,维修人员插拔连接器时产生的 ±8kV 接触放电,导致 MCU 输入引脚击穿,直接引发通讯中断、采集精度偏差超 10% 的故障;

潜在性失效:损伤较为隐蔽,测试阶段功能看似正常,却会在长期使用中逐渐出现性能退化。

某消费级芯片曾因版图中 ESD 器件与核心电路衬底耦合过强,用户使用半年后频繁死机,失效分析显示,是 ESD 造成的隐性衬底损伤在持续扩散。

这也意味着,缺乏可靠的 ESD 防护,芯片的良率、可靠性与市场竞争力便无从谈起。而芯片超过 70% 的 ESD 防护能力,恰恰在版图设计阶段就已注定。

二、从蓝图到现实:ESD 防护的 “理想” 与 “落地”

电路设计工程师通常会提供成熟的 ESD 保护电路方案,诸如经典的 GGNMOS、SCR 等结构。这些方案在原理图上堪称完美,勾勒出低阻泄放的理想路径。但这绝非终点,而是版图工程师将 “纸上蓝图” 转化为 “硅基现实” 的起点。

版图工程师的核心使命,便是让抽象的电路逻辑,在硅片上落地为可制造、能生效的物理结构。而 ESD 防护的效果,恰恰在这场 “转化” 中被重新定义。

这里藏着一个核心矛盾:电路设计追求 “功能正确”,只需逻辑连通、器件尺寸达标即可;版图设计则要实现 “性能落地”,布线是否对称、电流密度是否均匀、寄生效应是否可控 —— 这些物理细节,直接决定 ESD 保护电路在关键时刻能否 “扛住冲击”。

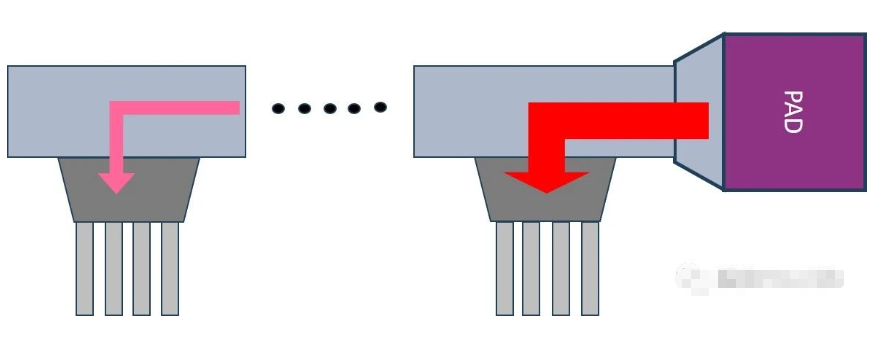

某芯片曾采用经典 GGNMOS 防护电路,原理图验证防护等级达 HBM 8kV,但版图设计时为节省面积,将原本整体的 ESD 器件拆分为两个分立单元分开放置。结果流片后实测仅能承受 2kV 静电,原因是 ESD 电流集中通过第一个器件,导致局部烧毁,第二个器件几乎未参与泄放 —— 再好的电路方案,也会因版图布局失误彻底失效。

三、版图工程师的 ESD 实战心法:五大核心准则

将 ESD 防护融入版图的每一处细节,需要版图工程师恪守五大核心准则,在微观世界中精雕细琢——

准则一:均衡分流 —— 规避 “电流拥堵” 的陷阱

ESD 电流本质是一股瞬时爆发的巨大能量流,版图设计的关键,是让这股能量均匀流过 ESD 保护器件中多个并联的指状晶体管。

某芯片初期采用单边接触叉指结构,且 Finger Width 设计低于晶圆厂ESD Rule 限值,ESD冲击时仅靠近电流入口的 3 根指状晶体管开启,瞬间因电流密度过高熔断;后续调整为双环虚指(Dummy Finger)对称布局,12 根指状晶体管同步导通,电流均匀分布,ESD 耐受电压从 1.5kV 直接提升至 6kV,而器件总宽度并未增加。

准则二:驯服寄生 —— 拆解 “隐形暗箭”

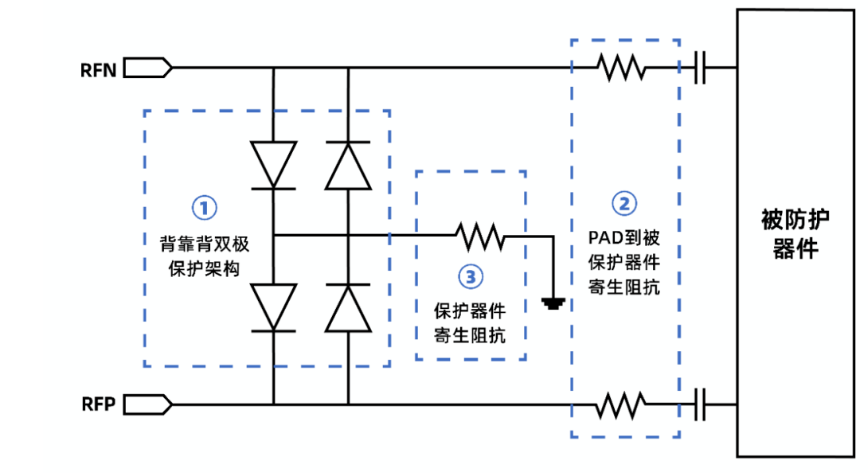

版图中的寄生电阻与寄生电感,是 ESD 防护的 “隐形暗箭”。某车载 ECU 的 PCB 版图中,ESD 器件与连接器距离达 8mm,35μm 铜轨引入的寄生电感达 40nH,12.5A ESD 电流冲击时额外压降超 500V,直接突破核心电路耐受极限。后续遵循 “3mm 距离原则” 缩短布线,寄生电感降至 1.5nH,额外压降减少 70%。这也印证了版图设计的核心对策:加宽金属线降低电阻,优先用高层厚金属部署关键布线,最大限度缩短 ESD 器件到焊盘的距离。

准则三:敬畏规则 —— 不止于 DRC 的底线

晶圆厂提供的设计规则检查(DRC),是版图可制造的 “最低标准”,而非 ESD 防护的 “最优准则”。某 14nm 工艺芯片的高速 I/O 金属布线过长,且未插入天线二极管,光刻阶段金属线收集的电荷直接击穿了连接的薄栅氧晶体管,导致流片良率下降 12%,后续通过跳线设计才规避了该风险。

针对 ESD 区域,版图工程师必须严守更严苛的 “ESD Rule”,比如 ESD 器件有源区到阱边缘的间距、接触孔密度等要求,通常远高于普通器件,目的就是强化器件鲁棒性。

准则四:模块隔离 —— 筑起 “安全护城河”

优秀的版图设计,离不开清晰的 “功能分区” 思维。某公司 RFID 芯片就在核心电路与 I/O/ESD 区域之间布设独立保护环,同时将芯片外围的 seal ring 纳入 ESD 泄放路径。

这种设计既抵御了闩锁效应(Latch-up),又隔离了噪声,确保 ESD 电流沿预设路径泄放,不闯入核心区域,最终让芯片 ESD 防护等级从行业普遍的 6kV 提升至 10kV 以上。

立体化ESD防护体系示意图

准则五:仿真验证 —— 织密最后的 “安全网”

版图绘制完成,并非工作的终点。某 HDMI 2.1 接口芯片初期未做 ESD 后仿真,版图中 ESD 器件寄生电容过大,导致 12Gbps 速率下眼高衰减 40%,误码率超标。

后续通过提取版图寄生参数(RC)反标回电路仿真,优化 ESD 器件布局与布线长度,最终眼图模板余量恢复至 25%,满足了传输要求。这也说明,后仿真与 PERC 专项检查,是排查泄放路径漏洞的关键。

四、进阶之道:性能、面积与可靠性的精妙平衡

版图设计从来不是单向的极致追求,而是一场精妙的平衡艺术。某7nm FinFET 工艺的 28Gbps SerDes 接口,就曾面临 “防护强则面积超” 的痛点。最终工程师采用 Sofics DTSCR 局部钳位结构,通过版图优化将寄生电容降至 80fF 以下,在芯片面积仅增加 3% 的情况下,实现了 CDM 500V 防护等级。这背后,是工程师与电路设计者深度协同的结果 —— 他们需洞悉芯片应用场景,在消费电子的常规防护与汽车电子的严苛要求之间,找到最优解。

结语:版图工程师 —— 芯片可靠性的终极守护者

当摩尔定律持续向纳米尺度纵深,芯片内部的电场强度愈发集中,器件结构也愈发脆弱,对 ESD 防护的要求便愈发严苛。版图工程师的角色,早已从单纯的 “绘图者”,进化为芯片 “可靠性设计师”。

理解 ESD 的致命威胁,意味着他们要将 “可靠性” 的基因,通过每一根金属线的排布、每一个接触孔的定位,深植于芯片的物理肌理之中。

驾驭版图与 ESD 的复杂关系,则要求他们兼具微观世界的极致细致与宏观布局的全局视野,既是恪守物理定律的严谨科学家,也是在方寸之间运筹帷幄的创意实践者。

当一颗芯片历经设计、制造、封装的漫长旅程,最终抵达用户手中,它能抵御住现实世界的每一次意外触碰,在电子设备中稳定运行数年甚至数十年 —— 这便是对版图工程师工作的最高致敬。他们,正是为芯片铸造生命 “金钟罩” 的幕后匠人。

魔乐社区(Modelers.cn) 是一个中立、公益的人工智能社区,提供人工智能工具、模型、数据的托管、展示与应用协同服务,为人工智能开发及爱好者搭建开放的学习交流平台。社区通过理事会方式运作,由全产业链共同建设、共同运营、共同享有,推动国产AI生态繁荣发展。

更多推荐

已为社区贡献8条内容

已为社区贡献8条内容

所有评论(0)