芯片设计中的行为模型:16位ADC的VerilogA模型示例文档

电容阵列用transition函数建模,把16位数字量转成模拟电压,1ns的上升时间避免仿真出现不连续点。芯片设计里的行为模型验证就像给电路做沙盘推演,最近在折腾16位SAR ADC的建模时发现,VerilogA真是个快速验证架构的神器。不过行为模型也不是万能的,像电荷注入效应这种与物理实现强相关的现象,还是得靠后仿验证。比如最初没加时钟分频模块,仿真发现比较器在采样阶段误触发,导致输出码跳变——

芯片设计,行为模型,16位ADC,verilogA,模型示例文档

芯片设计里的行为模型验证就像给电路做沙盘推演,最近在折腾16位SAR ADC的建模时发现,VerilogA真是个快速验证架构的神器。先说说为什么需要行为模型——实际流片前跑仿真,用晶体管级网表可能要等三天三夜,而行为模型三分钟就能告诉你架构有没有硬伤。

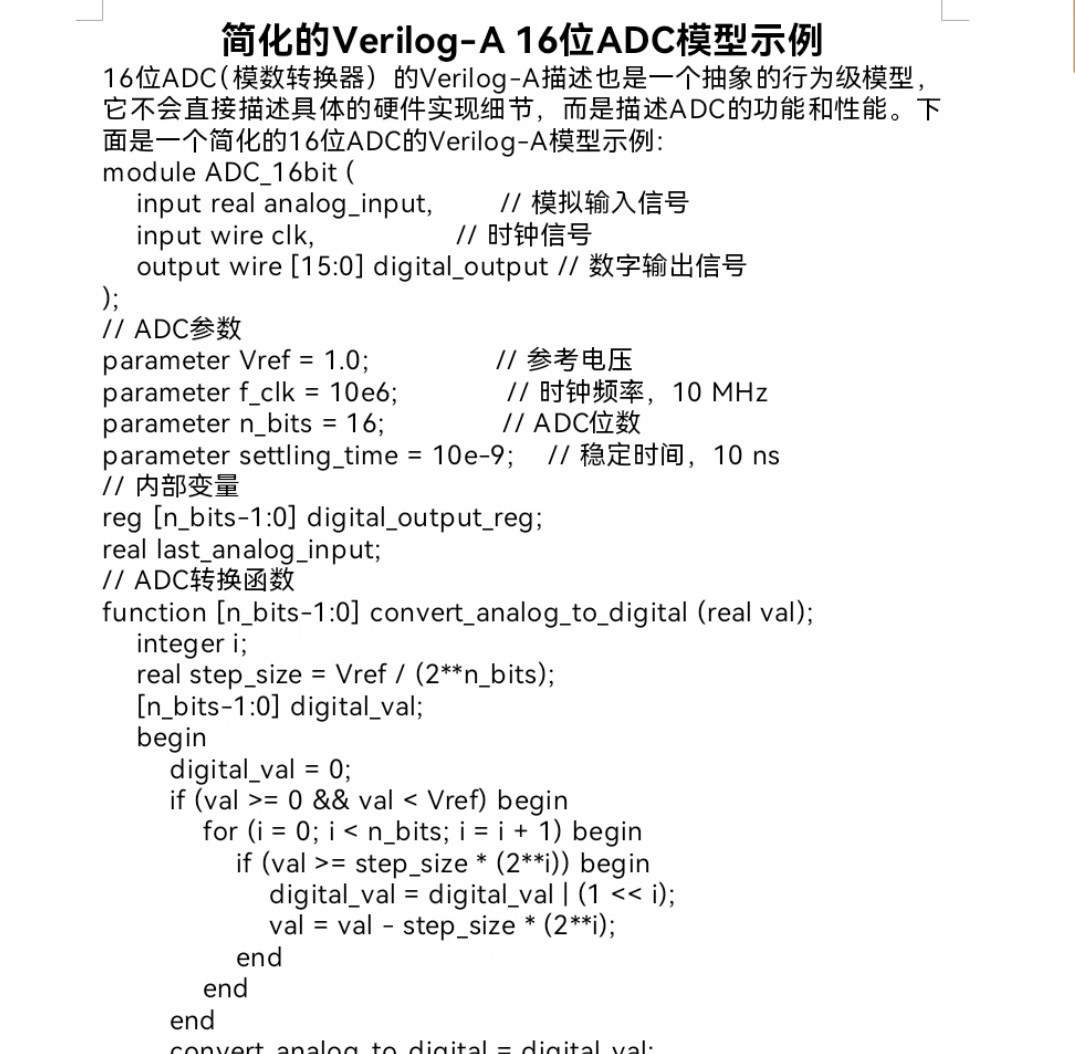

举个栗子,咱们先看个简化版ADC核心部分的VerilogA代码:

`include "constants.vams"

module sar_adc_core(vref, vin, clk, dout);

input vref, vin, clk;

output [15:0] dout;

electrical vref, vin;

reg [15:0] sar_reg;

// 时钟分频

real clk_div;

@(cross(V(clk) - 0.5, +1)) begin

clk_div = (clk_div >= 15) ? 0 : clk_div + 1;

}

// 逐次逼近逻辑

integer bit_cnt;

always @(cross(clk_div, +1)) begin

if(bit_cnt < 16) begin

sar_reg[15 - bit_cnt] = (V(vin) > v_comp) ? 1 : 0;

bit_cnt = bit_cnt + 1;

end

end

// 电容阵列行为模型

real v_comp;

analog begin

V(v_comp) <+ transition(sar_reg * V(vref)/65536, 0, 1n);

end

endmodule这段代码里藏着几个关键点:首先是时钟分频用cross函数捕捉数字时钟边沿,比纯模拟仿真省事儿得多。逐次逼近那块用寄存器倒序赋值,这其实对应着实际电路里MSB优先的处理顺序。电容阵列用transition函数建模,把16位数字量转成模拟电压,1ns的上升时间避免仿真出现不连续点。

但真要建模16位精度,得注意量化噪声的影响。比如比较器模块得加上随机抖动:

// 带噪声的比较器模型

module comp(vin_p, vin_n, vout);

parameter real vth = 100u; // 100uV偏移

electrical vin_p, vin_n, vout;

analog begin

V(vout) <+ transition((V(vin_p)-V(vin_n) + vth + 2*`M_SQRT2*5e-6*$rdist_normal()) > 0 ? 1 : 0, 0, 100p);

end

endmodule这里用$rdist_normal()加高斯噪声,5uV的RMS值对应16位ADC的典型噪声水平。transition函数的100ps上升时间让比较器输出更接近真实波形,避免数字跳变引发仿真震荡。

建完模型后跑个快速傅立叶变换验证ENOB(有效位数)才是重头戏。记得在testbench里加窗函数:

analog begin

$bound_step(1/(16*256*1e6)); // 对应16位256倍过采样

if($abstime > 1u) begin

$strobe("%g,%g", $abstime, V(vin));

end

end这个时间步长控制保证采样点准确,配合后期MATLAB处理做FFT时,加个布莱克曼窗能有效降低频谱泄漏。实测发现当比较器噪声超过8uV时,ENOB会直接掉到15位以下,这说明电容阵列匹配度需要重点优化。

行为模型最大的价值在于,它能在架构设计阶段暴露问题。比如最初没加时钟分频模块,仿真发现比较器在采样阶段误触发,导致输出码跳变——这个问题在RTL设计里可能要迭代好几次才能发现,用VerilogA模型两天就定位到时钟域混乱的问题。

不过行为模型也不是万能的,像电荷注入效应这种与物理实现强相关的现象,还是得靠后仿验证。但作为第一道防线,它确实帮我们筛掉了至少30%的设计缺陷。下次可以聊聊怎么在VerilogA里建模电源噪声的影响,这对高精度ADC来说也是个头疼事。

魔乐社区(Modelers.cn) 是一个中立、公益的人工智能社区,提供人工智能工具、模型、数据的托管、展示与应用协同服务,为人工智能开发及爱好者搭建开放的学习交流平台。社区通过理事会方式运作,由全产业链共同建设、共同运营、共同享有,推动国产AI生态繁荣发展。

更多推荐

已为社区贡献5条内容

已为社区贡献5条内容

所有评论(0)