你的芯片为何在静电面前不堪一击——高压驱动IC的ESD失效分析与防护全解析

摘要:静电放电(ESD)已成为高压驱动芯片的重要失效因素,特别是OLED显示和电源管理芯片中隔离地线导致的内部电路损伤问题日益突出。研究发现,ESD电流会绕过防护电路,通过数字-模拟接口造成栅氧层击穿,使泄漏电流激增20倍以上。本文提出综合治理方案:采用全路径I/O保护、增加电源轨钳位电路,并通过双向二极管串连接隔离地线。实验证明该方案能显著提升ESD耐受能力,为高压混合电压芯片设计提供系统级防护

静电放电(ESD)是集成电路的“隐形杀手”,尤其是在高压驱动芯片中,即便在输入输出端部署了防护电路,内部电路仍可能遭受不可见的损伤。近年来,随着OLED显示面板、电源管理等高压混合电压芯片的广泛应用,ESD引发的内部损伤问题愈发显著。本文将为你深入解析高压驱动IC中的ESD失效机理,并给出经实验验证的有效防护方案。

一、为何对芯片如此危险?

静电放电指的是当带电的人体、工具或设备接触芯片时,存储的电荷瞬间释放的过程。常用的人体模型(HBM)可模拟人手触摸芯片引脚的放电情况,其电压可达数千伏,持续时间仅纳秒级,但电流峰值却可能高达数安培。

在许多高压驱动芯片内部,往往同时存在着工作电压迥异的两大电路阵营:高压模拟电路与低压数字电路。在传统设计中,为了抑制噪声干扰,常将两者的地线(GND)与电源线(VDD)予以隔离。然而,这种隔离却在不经意间为ESD电流开辟了“迂回路径”,最终导致内部接口电路受损。

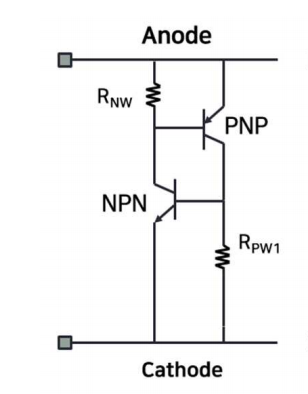

(传统可控硅整流器的电路实现)

二、内部电路因何受损?——失效机理深度剖析

关键症结:隔离的地线与电源线

在研究的OLED高压驱动IC中,初始设计将数字地(GNDD)与模拟地(GNDA)物理隔开。当执行如VDDD至GNDA这类跨电压域的ESD测试时,ESD电流无法经由预设的保护通道泄放,只得强行穿越内部电路,引发栅氧层击穿、金属导线熔断等损伤。

损伤高发区:数字-模拟接口电路

借助扫描电子显微镜(SEM)和光学显微镜(OM)的观测,研究团队发现损伤集中出现在低压PMOS与高压NMOS相连的接口区域。特别是高压NMOS的栅氧层,由于其自身结构脆弱,在ESD电流冲击下极易发生破坏。

实测数据:泄漏电流激增超20倍

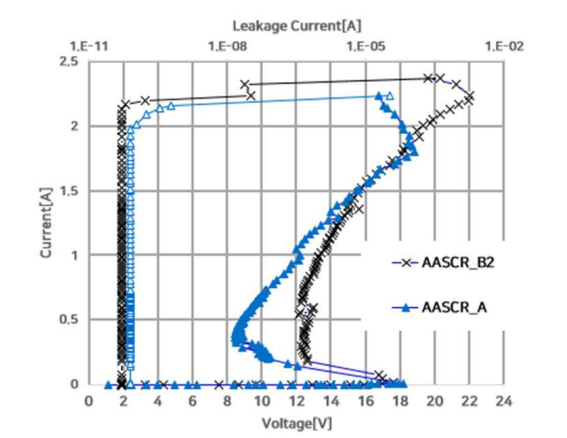

ESD测试后,VDDD与GNDA之间的泄漏电流从正常水平骤增超过20倍,这表明芯片内部已发生实质性损伤。原始芯片的HBM ESD耐受电压仅为1.0kV,远低于业界普遍要求的2.0kV标准。

(SCR的TLP I-V特性)

- 如何构建真正可靠的ESD防护体系?——三大方案对比

方案一:局部增强法——在接口处增设栅极保护电路

该方法虽能局部强化输入级的栅氧保护,但未能从根本上解决ESD电流的全局泄放路径问题,属于局部补救措施。

方案二:全局布局法——通过ESD单元互联隔离的地/电源线

此方案被视为当前的高效策略。它通过双向二极管串或类似ESD器件连接隔离的地线,为ESD电流提供规范的低阻抗通路,有效阻止其侵入内部电路。

方案三:本研究采用的优化方案——综合治理策略

在第二代芯片设计中,团队实施了以下综合改进:

所有I/O引脚均采用全路径保护设计(即在Pad至VDD和Pad至VSS均设置钳位电路)。

在低压数字电路区域新增VDDD至GNDD的电源轨ESD钳位电路。

使用双向多二极管串连接GNDD与GNDA,建立安全的ESD电流泄放通道。

鉴于VDDA与VDDD之间存在较大压差,保持两者隔离,未直接连接

- 致芯片设计师:ESD防护需具备系统视野

1、避免地线简单隔离:在混合电压芯片中,不同地线之间应通过专用ESD单元连接。

2、电源轨必须加钳位电路:每个电压域都应部署VDD-to-VSS保护装置。

3、I/O保护要双向兼顾:避免仅保护至VSS而忽略至VDD的路径。

4、接口电路是重点保护区:数字与模拟交接处应增加缓冲保护结构。

5、采用可集成的ESD器件:如二极管串、SCR等,面积小、效果优。

ESD防护不是“加几个二极管”那么简单,尤其是对于高压、混合电压的驱动芯片。真正的可靠性来自于全局电流路径设计与内部接口的协同保护。通过科学的失效分析与系统级防护策略,可以有效将芯片的ESD耐受能力提升至行业标准以上,保障产品在制造、组装及终端使用中的稳健运行。

魔乐社区(Modelers.cn) 是一个中立、公益的人工智能社区,提供人工智能工具、模型、数据的托管、展示与应用协同服务,为人工智能开发及爱好者搭建开放的学习交流平台。社区通过理事会方式运作,由全产业链共同建设、共同运营、共同享有,推动国产AI生态繁荣发展。

更多推荐

已为社区贡献8条内容

已为社区贡献8条内容

所有评论(0)