Verilog语法学习EP1:Verilog语法学习的环境配置基于vscode+modelsim

本文介绍了在没有FPGA硬件的情况下,使用Modelsim仿真工具和VSCode编辑器学习Verilog语法的方法。推荐安装Modelsim2020.4SE版本和VSCode的Verilog插件,建议在VSCode中新建专用配置文件管理开发环境,以便实现代码补全功能。文中参考了北京交通大学李金城老师的Verilog入门课程,并对比了不同编辑器(UltraEdit和VSCode)的使用效果。

一、前言

学习FPGA,在没有硬件的情况下,我们采用modelsim+vscode先进行Verilog语法学习,即仿真与文本编辑,本套学习笔记采用北京交通大学李金城老师的Verilog零基础入门课程:

一、modelsim的安装

modelsim 2020.4SE安装教程超详细(仅供学习使用)_modelsim安装教程-CSDN博客

上述安装教程很仔细。建议采用。

二、VsCode的插件安装

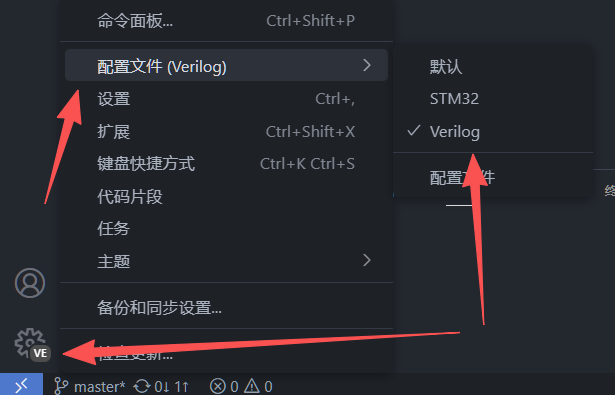

建议大家现在VsCode中新建一个配置文件,然后把插件装在这个配置文件下,专门用于编写Verilog代码,这样能有效地避免插件冲突。开发环境进行规范化管理。

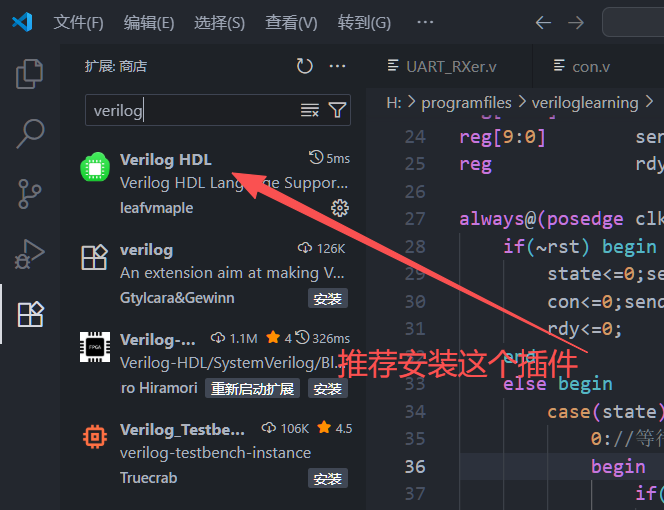

在扩展中,搜索verilog,市场自动给你推荐安装量较高的插件,选择其一安装即可。

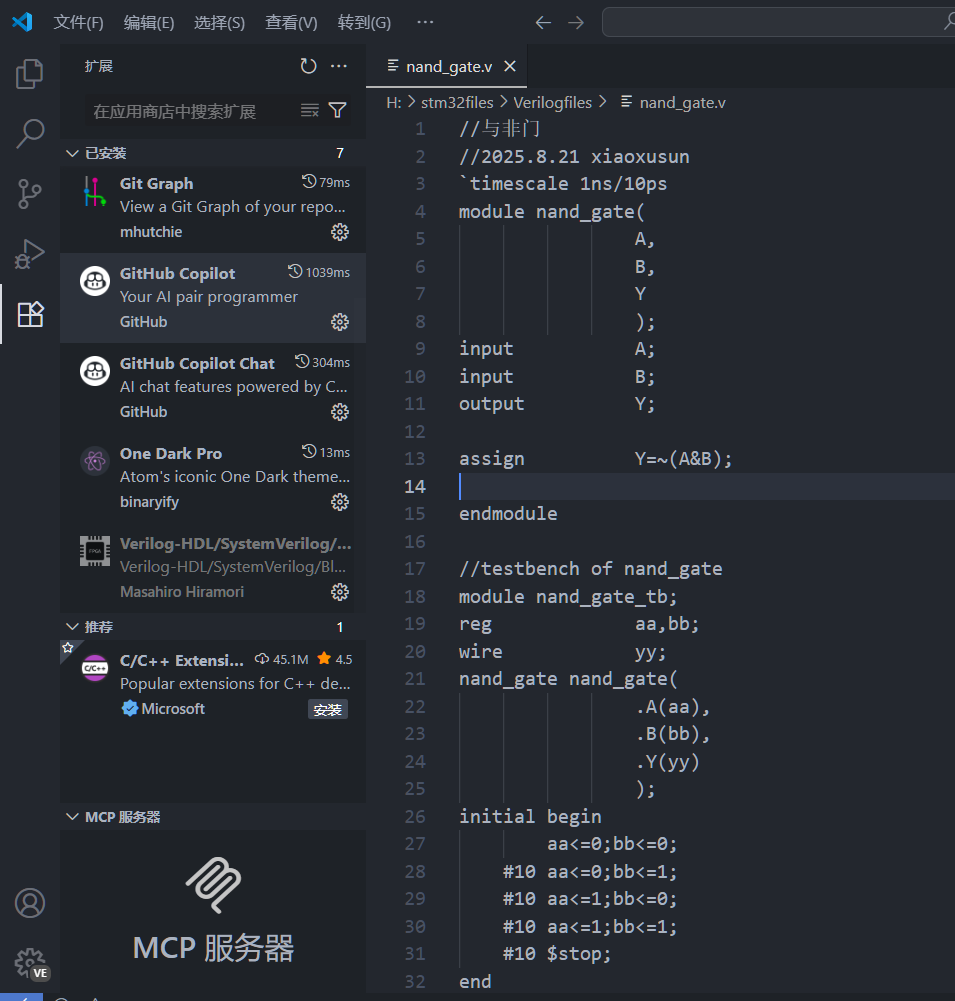

没启用插件的效果如下:

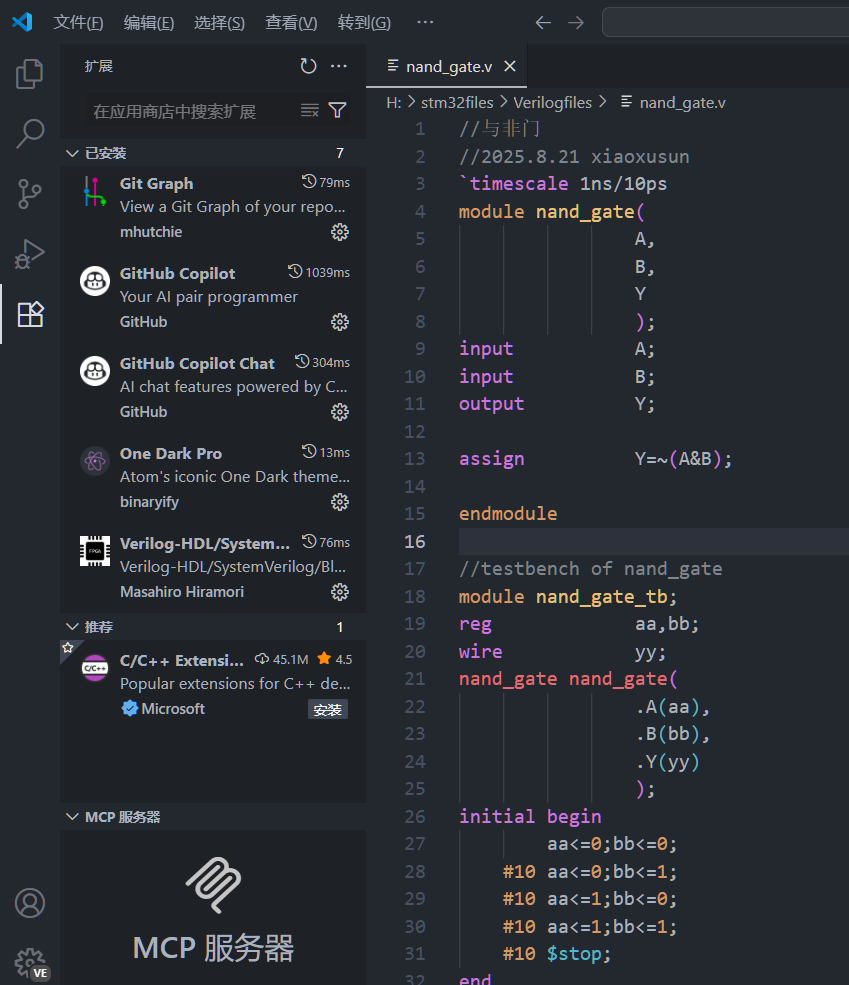

启用插件的效果如下:

实际操作中,能很方便地实现代码补齐,方便我们学习。

在课程中,李老师采用的文本编辑器是UltraEdit且安装了Verilog语法相关的插件,采用VsCode进行文本编辑也是相当方便的。

魔乐社区(Modelers.cn) 是一个中立、公益的人工智能社区,提供人工智能工具、模型、数据的托管、展示与应用协同服务,为人工智能开发及爱好者搭建开放的学习交流平台。社区通过理事会方式运作,由全产业链共同建设、共同运营、共同享有,推动国产AI生态繁荣发展。

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)