深入解析多路选择器(MUX):计算机组成原理的核心组件

本文系统介绍了多路选择器(MUX)的原理与应用。MUX作为基础组合逻辑器件,通过选择信号实现多路数据路由,其核心结构包括输入、选择线和输出端。文章详细阐述了MUX的分类(2:1至n:1)、级联扩展方法,以及在CPU数据通路、总线控制、逻辑函数生成等场景的关键应用。通过对比三态门技术,分析了MUX的隔离优势。同时探讨了FPGA中的高效实现方式(LUT级联)和集成电路优化技术,并展望了高集成度、低功耗

摘要:多路选择器(Multiplexer, MUX)是数字电路中的基础组合逻辑器件,通过选择信号动态路由数据,实现高效资源复用。本文将系统介绍其原理、分类、应用及现代实现技术,并扩展FPGA设计、逻辑函数生成等进阶知识。

1. MUX的核心原理与结构

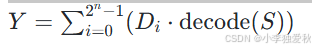

定义:MUX是一种多输入、单输出的组合逻辑电路,通过 n 位选择线(Select Lines)从 2^n 路输入中选择一路输出到公共通路 。其数学表示为:

其中 S 为选择信号编码,Di 为输入数据 。

典型结构(以4选1 MUX为例):

- 输入:D0,D1,D2,D3

- 选择线:S0,S1(2位编码)

- 输出:Y

| S1 | S0 | Y |

|---|---|---|

| 0 | 0 | D0 |

| 0 | 1 | D1 |

| 1 | 0 | D2 |

| 1 | 1 | D3 |

硬件实现:

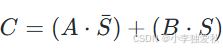

-

基础2:1 MUX可通过逻辑门实现:

-

Verilog示例:

module mux2(input A, B, S, output C); assign C = S ? B : A; // S=0输出A,S=1输出B endmodule

2. MUX的分类与扩展设计

按输入规模分类 :

- 2:1 MUX:1位选择线,2路输入(如选择寄存器输入)

- 4:1 MUX:2位选择线,4路输入(常用作存储器地址选择)

- 8:1 MUX:3位选择线,8路输入(复杂系统通信)

- n:1 MUX:选择线位数 m = log2(n)

级联扩展:

- 小规模MUX可级联构建更大选择器,例如:

- 用 2个4选1 MUX + 1个2选1 MUX 实现8选1功能

- 树形结构(MUX Tree)减少延迟,优化布线

3. 关键应用场景

-

CPU数据通路:

- 选择寄存器输入到ALU(如Select=0时选A通道,Select=1时选B通道)

- 指令译码时根据操作码(Opcode)路由控制信号

-

总线与存储器:

- 替代三态门实现总线共享(需配合多路分配器Demux),避免多个使能信号冲突

- 内存地址映射时选择不同地址源(如8位4选1 MUX路由内存数据到ALU)

-

信号转换与逻辑生成:

- 并行转串行:通过时序控制选择线,按序输出并行数据

- 实现任意逻辑函数:固定MUX输入为0/1,选择线作为变量(如用74HC151实现3变量函数)

-

嵌入式系统:

- 彩灯控制器中按选择信号切换灯光模式

- FPGA中基于查找表(LUT)构建可编程逻辑

4. MUX vs. 三态门:技术对比

| 特性 | MUX | 三态门 |

|---|---|---|

| 实现方式 | 纯组合逻辑(与或门) | 逻辑门 + 高阻态开关 |

| 冲突风险 | 无短路风险(输入物理隔离) | 需严格避免多个使能同时有效 |

| 扩展性 | 可级联支持大规模输入 | 依赖总线负载能力 |

5. 现代实现技术:FPGA与集成电路

FPGA核心资源:

- LUT6 + MUXF7/MUXF8:

- MUX4:1个LUT6实现(4输入+2地址线)

- MUX8:2个LUT6 + 1个MUXF7

- MUX16:4个LUT6 + 2个MUXF7 + 1个MUXF8

- 优势:固定MUX结构比LUT6直接实现更节省资源,布线延迟一致

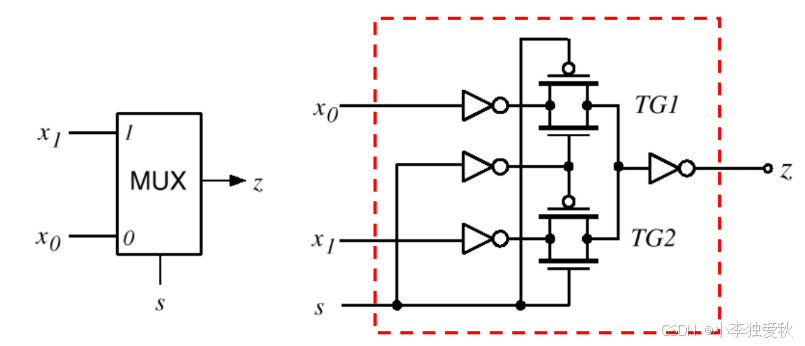

集成电路优化:

- CMOS工艺构建紧凑型2:1 MUX,传输门设计降低功耗

- 标准芯片如74HC153(4:1 MUX)、74HC151(8:1 MUX)

6. 前沿趋势与挑战

- 高集成度:纳米工艺下MUX与存储器、ALU的融合设计

- 低功耗优化:采用传输门(Transmission Gate)替代逻辑门减少动态功耗

- 可重构性:FPGA中MUX支持动态重配置,适应多场景需求

结语:MUX通过硬件级数据路由实现了计算机系统的“分时复用”与“资源复用” ,从基础数据选择到FPGA可编程逻辑,其设计思想深刻影响着数字系统演进。理解MUX的底层原理与扩展应用,是掌握计算机体系结构的关键一步。

魔乐社区(Modelers.cn) 是一个中立、公益的人工智能社区,提供人工智能工具、模型、数据的托管、展示与应用协同服务,为人工智能开发及爱好者搭建开放的学习交流平台。社区通过理事会方式运作,由全产业链共同建设、共同运营、共同享有,推动国产AI生态繁荣发展。

更多推荐

已为社区贡献34条内容

已为社区贡献34条内容

所有评论(0)