为什么在芯片互连中,介质的k值一直在降低?

芯片互连中介质k值降低主要是为了减小RC延迟。随着CMOS技术进入45nm以下节点,互连寄生电容成为性能瓶颈。电容公式C=ε*A/d表明,降低介电常数(k值)能有效减小电容。因此工艺节点越先进,k值从2.7逐步降至2.1以下。常见低k介质包括有机聚合物、多孔硅基材料等,通过降低介电常数来提升芯片性能。

·

知识星球(星球名:芯片制造与封测技术社区,星球号:63559049)里的学员问:为什么在芯片互连中,介质的k值一直在降低?有哪些低k的介质?

互连介质的k值为什么在降低?

随着 CMOS 技术进入 45nm 及以下节点,互连 RC 延迟成为关键瓶颈,RC延迟见文章:

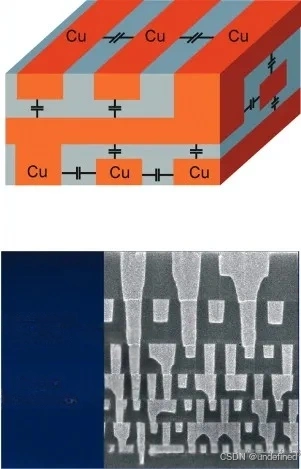

如上图,金属线与金属线之间夹着介质层,类似于一个电容,而寄生电容是RC延迟的主要来源。

而电容的表达式为:

C=ε*A/d

C:电容值

ε:介电常数

A:电极面积 (互连金属线的宽度)

d:金属线之间的距离

如表达式可以看出,介电常数越大,电容越大,RC延迟越严重。

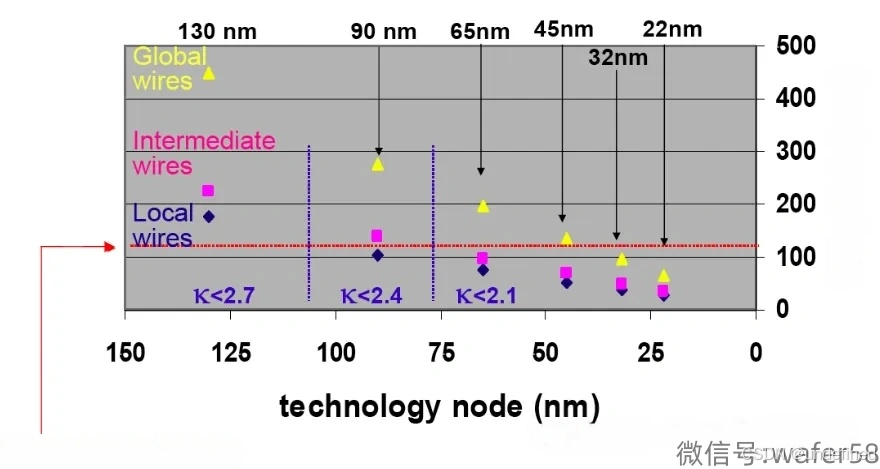

芯片节点与k值的关系? 如上图,k值逐渐由小于2.7降到小于2.1,

如上图,k值逐渐由小于2.7降到小于2.1,

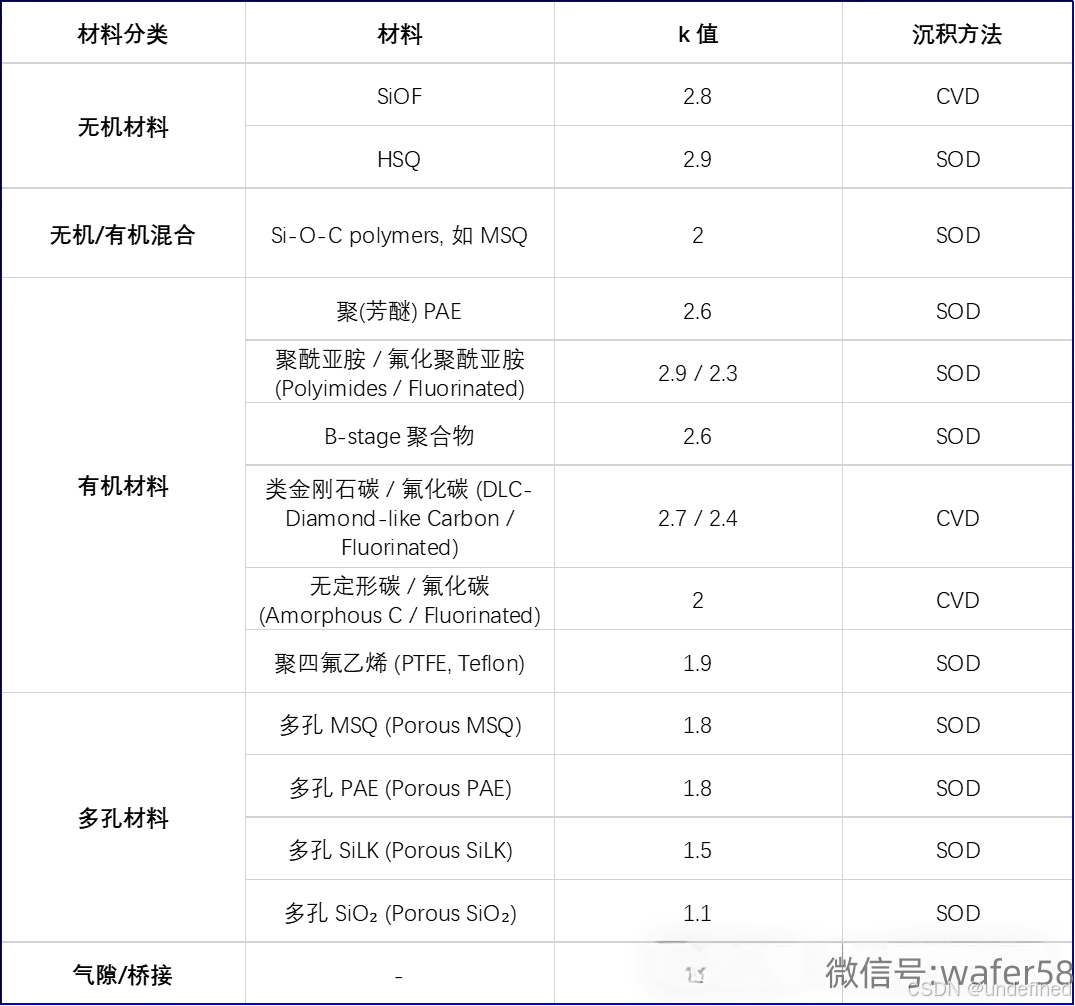

各类低k介质有哪些?

魔乐社区(Modelers.cn) 是一个中立、公益的人工智能社区,提供人工智能工具、模型、数据的托管、展示与应用协同服务,为人工智能开发及爱好者搭建开放的学习交流平台。社区通过理事会方式运作,由全产业链共同建设、共同运营、共同享有,推动国产AI生态繁荣发展。

更多推荐

已为社区贡献19条内容

已为社区贡献19条内容

所有评论(0)