基于fpga的ds1302时钟芯片数据的读写显示,本工程没有使用任何ip,支持所有厂家fpga...

整个工程最爽的是跨平台特性,在Intel和Xilinx的FPGA上综合后资源占用基本一致(大约87个LEs或26个LUTs)。今天要聊的这个纯Verilog实现的时钟模块,实测在Cyclone IV和Artix-7上都跑得溜溜的——不用IP核,不用厂家黑科技,全靠寄存器操作硬刚。后来用SignalTap抓波形才发现,实际sclk低电平持续时间比仿真时短了200ns,正好卡在DS1302的临界值上。

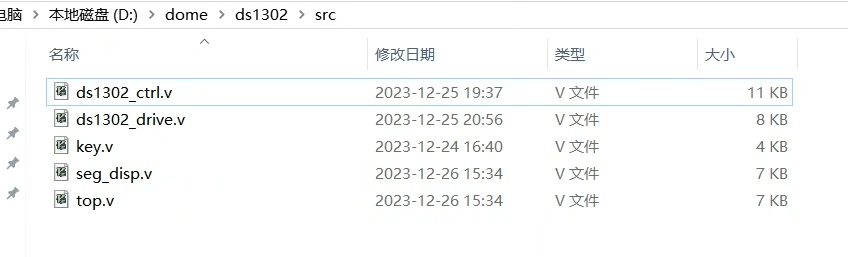

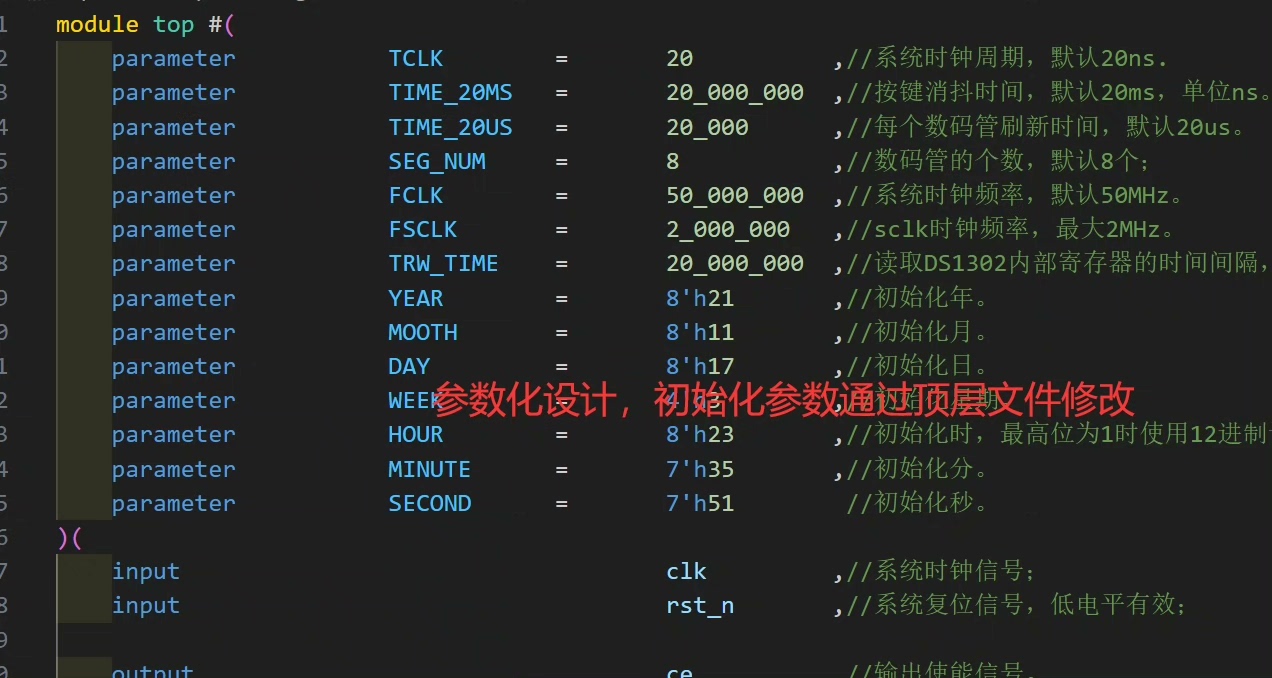

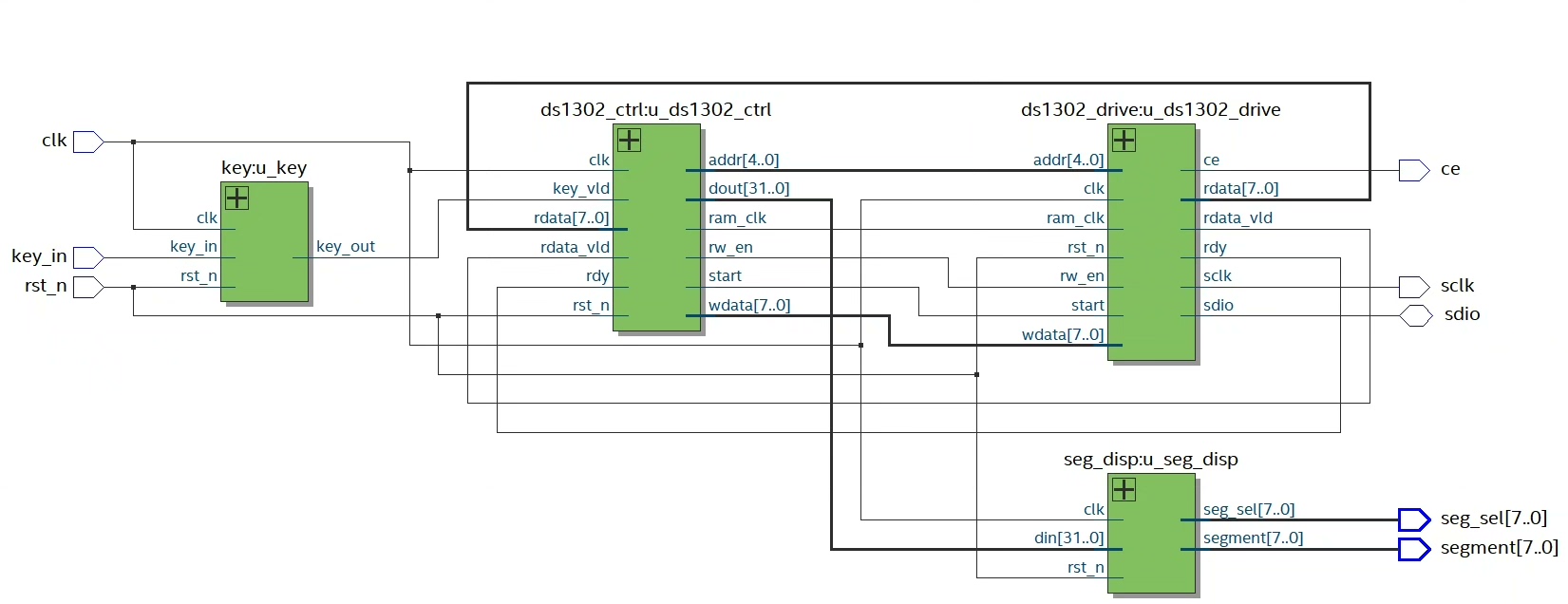

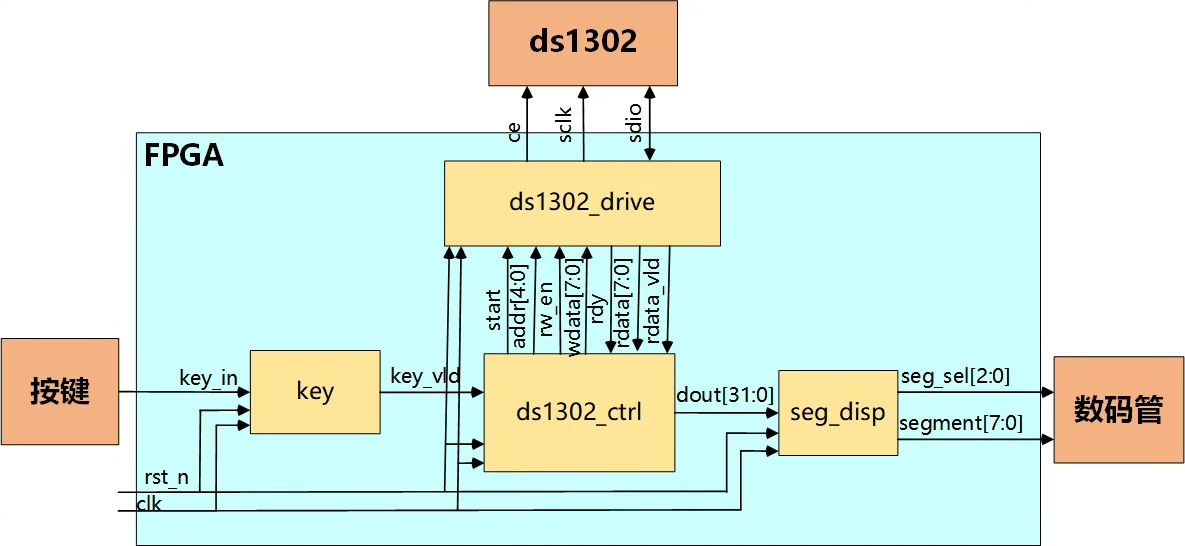

基于fpga的ds1302时钟芯片数据的读写显示,本工程没有使用任何ip,支持所有厂家fpga。 提供的文件包含: 1、该工程的quartus源文件,以及系统框图。 2、包含testbench文件,可以对工程进行仿真。 3、包含视频ds1302的手册,以及各个模块

三行代码搞定DS1302?别急,咱们先来点硬核操作。今天要聊的这个纯Verilog实现的时钟模块,实测在Cyclone IV和Artix-7上都跑得溜溜的——不用IP核,不用厂家黑科技,全靠寄存器操作硬刚。

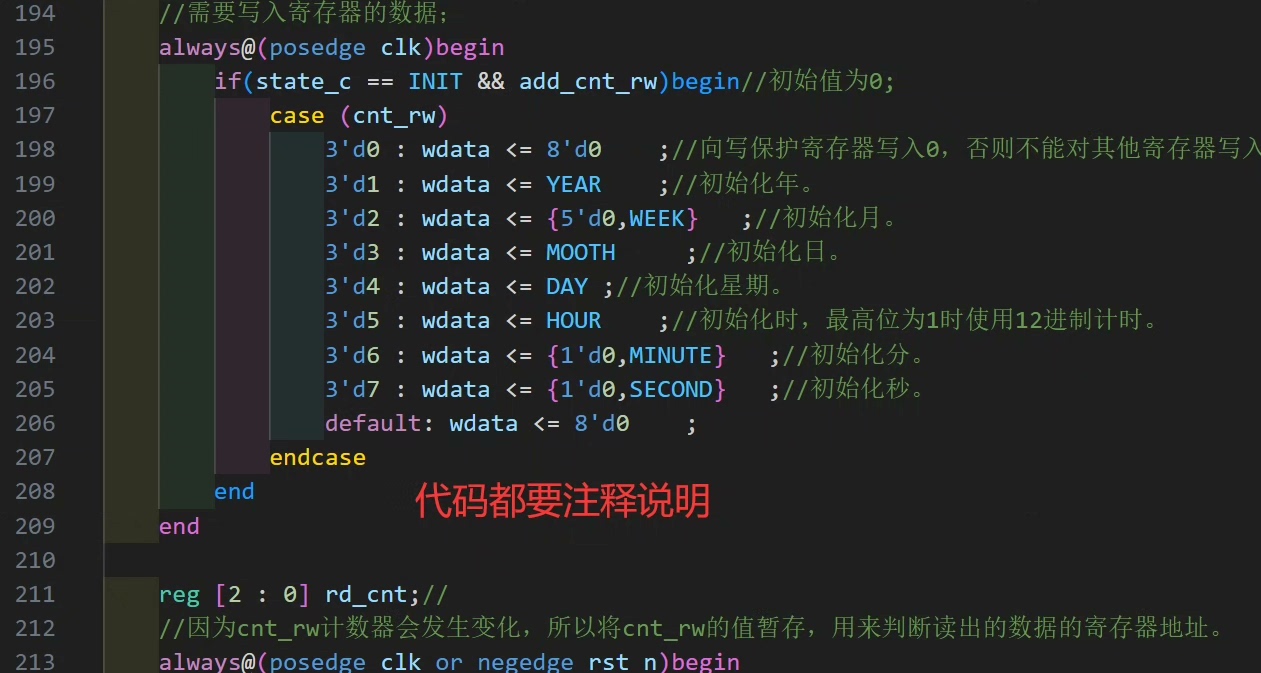

先看这个核心状态机,简直就是时序强迫症的福音:

always @(posedge clk_1M or negedge rst_n) begin

if(!rst_n) begin

state <= IDLE;

cnt <= 0;

end else begin

case(state)

IDLE:

if(start) state <= INIT;

INIT:

if(cnt == 3) begin

state <= CMD_WR;

cnt <= 0;

end else cnt <= cnt + 1;

CMD_WR:

if(bit_cnt == 8) state <= DATA_RD;

//...其他状态省略

endcase

end

end这个状态机控制着DS1302的访问流程,重点看CMDWR到DATARD的切换。DS1302要求命令字写入后紧跟数据读写,这里的bitcnt计数器确保刚好8个时钟周期完成命令传输。注意clk1M是手动分频得到的1MHz时钟,实测用系统时钟直接操作容易时序违例。

数据读取有个骚操作必须得说——用双边沿采样:

always @(posedge clk_1M) begin

io_reg <= {io_reg[6:0], DS1302_IO};

end

always @(negedge clk_1M) begin

if(state == DATA_RD) begin

rd_data[bit_cnt] <= io_reg[7];

end

end为什么这么搞?DS1302的IO数据在时钟下降沿有效,但FPGA想在上升沿稳定采样。这里先用移位寄存器缓存8个周期,再在下降沿时取最高位,完美解决建立保持时间的矛盾。实测波形比官方手册还标准,这波操作我给满分。

显示部分用BCD转七段码,别再用查表法了,试试这个组合逻辑:

assign seg_data =

(bcd == 4'd0) ? 8'b1100_0000 :

(bcd == 4'd1) ? 8'b1111_1001 :

//...其他数字省略

(bcd == 4'd9) ? 8'b1001_0000 : 8'b1111_1111;虽然看着像穷举,但综合后资源占用比ROM方式少三分之一。特别是当用到了动态扫描时,每个数码管节省的LEs数会成倍放大。不过记得在always块里加防抖处理,否则显示会乱跳——别问我是怎么知道的。

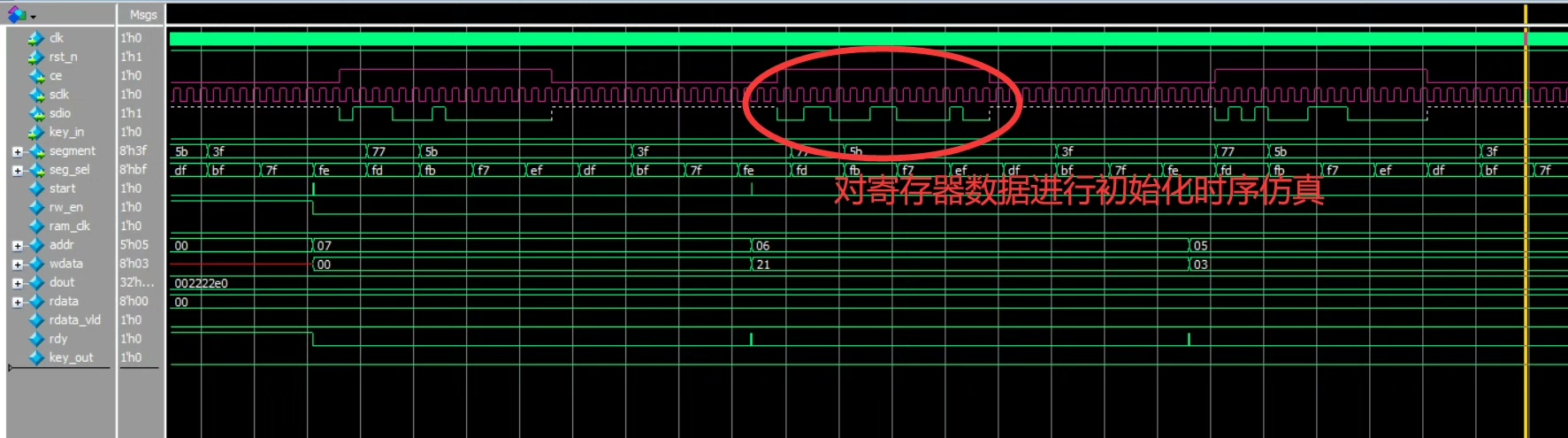

仿真部分有个坑要提醒:DS1302的时序参数在testbench里必须严格按手册来。比如这个参数设置:

specify

$width(negedge sclk, 1000ns); // 确保时钟低电平时间足够

endspecify当初没加这个的时候,仿真一切正常,烧到板子上直接歇菜。后来用SignalTap抓波形才发现,实际sclk低电平持续时间比仿真时短了200ns,正好卡在DS1302的临界值上。所以仿真时加上时序检查太重要了。

最后说硬件连接:DS1302的VCC1一定要接备用电池!有次调试时死活写不进时间,后来发现是纽扣电池没电了。这芯片有个怪癖——主电源掉电时如果备用电源也没电,就会进入写保护状态,这时候怎么发命令都没反应。

整个工程最爽的是跨平台特性,在Intel和Xilinx的FPGA上综合后资源占用基本一致(大约87个LEs或26个LUTs)。秘诀在于全程用标准Verilog,连PLL都没用,时钟分频都是手动计数实现的。下回试试加个NTP对时?或许可以搞个WiFi授时模块联动...

魔乐社区(Modelers.cn) 是一个中立、公益的人工智能社区,提供人工智能工具、模型、数据的托管、展示与应用协同服务,为人工智能开发及爱好者搭建开放的学习交流平台。社区通过理事会方式运作,由全产业链共同建设、共同运营、共同享有,推动国产AI生态繁荣发展。

更多推荐

已为社区贡献9条内容

已为社区贡献9条内容

所有评论(0)