揭秘芯片测试中的“心跳节拍”:Timing的奥秘

如果说Pattern是测试的“语言”,那么Timing就是测试的“心跳”

大家好,我是硅言。昨天我们聊了芯片测试中的Pattern(测试向量)半导体新人必看!芯片测试中的“神秘代码”Pattern,到底是什么?,今天我们来探索另一个核心概念——Timing(时序)。如果说Pattern是测试的“语言”,那么Timing就是测试的“心跳”。它决定了信号何时发出、如何传输、能否被准确捕获,稍有偏差,轻则性能受损,重则功能崩溃。接下来,让我们一同深入Timing的微观世界!

芯片测试中的Timing是什么?

在芯片测试中,Timing指的是信号在电路中传输的时间关系。它涉及时钟信号的同步性、数据信号的延迟与稳定性,以及信号边沿的精准控制。就像交响乐团的指挥棒,Timing协调着芯片内部亿万晶体管的工作节奏,确保数据在正确的时刻被采样和处理。若时序失控,轻则导致性能下降,重则引发功能错误,甚至芯片失效。有关Timing的基本概念:

- 周期(Cycle):ATE运行Pattern是以周期为单位的,Cycle反映Pattern的运行速度。

- 沿(Edge):在一个周期内,数据出现或改变的时刻点,包括输入时间沿、比较时间沿。

- 波形格式(Format):按时序输入给DUT的Pattern,直观看就是高低电平沿时间轴的变化,即波形(Waveform)。

如下是NI平台提供的波形格式,Non-Return (NR) 、Return to Low (RL) 、Return to High (RH) 和Surround by Complement (SBC)

某些ATE可能提供更灵活的方式供我们定义波形格式,比如在时刻点自由定义信号的升降以及组合方式。

- 输出采样(Strobe):可在固定的时刻点对输出电平采样比较,根据预先设定的VOL/VOH电平来判断输出信号的高低。

Timing的关键参数

- 脉冲宽度(Pulse Width):高电平或低电平持续的时间,用于时钟(clk)、片选(cs)等信号。

- Tco(时钟到输出延迟):从时钟触发到数据输出的总延迟,包括逻辑门延迟和缓冲器延时。

- 建立时间(Setup Time):输入信号在某一时刻点之前,必须维持设定值的最小时间,参考时刻点通常是时钟信号的上升沿或下降沿。

- 保持时间(Hold Time):输入信号在某一时刻之后,必须维持设定值的最小时间,参考时刻点通常是时钟信号的上升沿或下降沿。

- 时钟抖动(Jitter)与偏斜(Skew):抖动是时钟周期的随机波动,偏斜是时钟到达不同模块的时间差,两者如同心跳不齐与交通堵塞,威胁时序完整性。

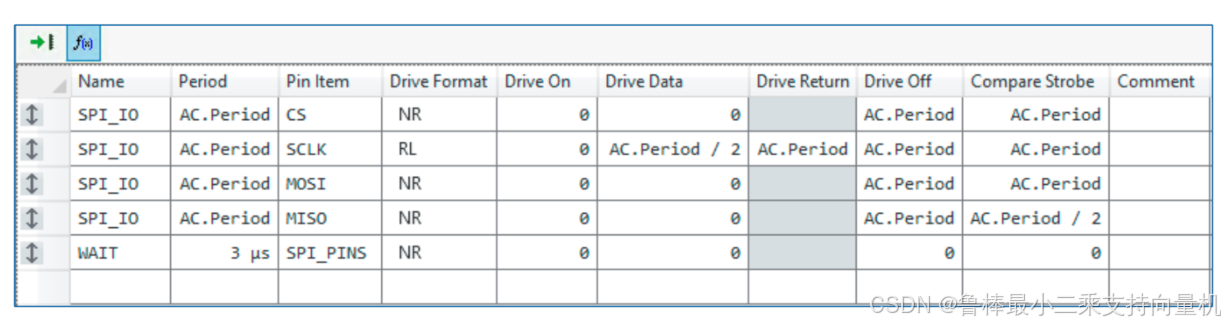

如图是使用NI设备定义的Timing:

从设计阶段的静态时序分析(STA),到测试阶段的ATE精准控制,Timing贯穿芯片生命周期的每个环节。它不仅是技术参数,更是一门平衡速度、功耗与可靠性的艺术。如果你对Timing有更多疑问,欢迎在评论区留言。

关注硅言芯语,带你解锁半导体行业的全部秘密!

⚠️ 免责声明:

本文内容综合公开报道、行业分析及第三方研究,信息存在时效性局限,技术描述可能存在专业偏差,部分含推测性表述,如有疏漏请联系修正。

🛡️ 版权声明:

未经许可禁止商用,转载需注明出处。

魔乐社区(Modelers.cn) 是一个中立、公益的人工智能社区,提供人工智能工具、模型、数据的托管、展示与应用协同服务,为人工智能开发及爱好者搭建开放的学习交流平台。社区通过理事会方式运作,由全产业链共同建设、共同运营、共同享有,推动国产AI生态繁荣发展。

更多推荐

已为社区贡献12条内容

已为社区贡献12条内容

所有评论(0)