IS61LV25616芯片技术手册

256K*16告诉异步CMOS静态RAM(支持3.3V)特性高速访问时间:8,10,12和15nsCMOS 低功耗运行兼容TTL接口电平单3.3V±10%供电全静止操作:不需要提供时钟或者刷新三态输出上下字节的数据控制工业温度内可用描述ICSILS61LV25616(后面简称25616)芯片是一个高速的,4 194 304 bit静态RAM,其中包含262144个16位...

256K*16告诉异步CMOS静态RAM(支持3.3V)

特性

- 高速访问时间:8,10,12和15ns

- CMOS 低功耗运行

- 兼容TTL接口电平

- 单3.3V±10%供电

- 全静止操作:不需要提供时钟或者刷新

- 三态输出

- 上下字节的数据控制

- 工业温度内可用

描述

ICSILS61LV25616(后面简称25616)芯片是一个高速的,4 194 304 bit静态RAM,其中包含262144个16位字长。它是通过ICSI高性能CMOS技术制造而成。这种高度可靠的工艺与电路设计技术相结合,制造出高性能,低功耗的设备。

当CE‾\overline{\rm{CE}}CE是电平时(未被选中),这个设备假定在等待模式状,功耗可以降低到CMOS输入水平。

提供简单内存扩展,设置芯片使能和输出使能的输入信号,分别为CE‾\overline{\rm{CE}}CE和OE‾\overline{\rm{OE}}OE。低电平写入使能WE‾\overline{\rm{WE}}WE在内存的读取与写入时都有效。允许高字节(UB‾\overline{\rm{UB}}UB)和低字节(LB‾\overline{\rm{LB}}LB)访问。

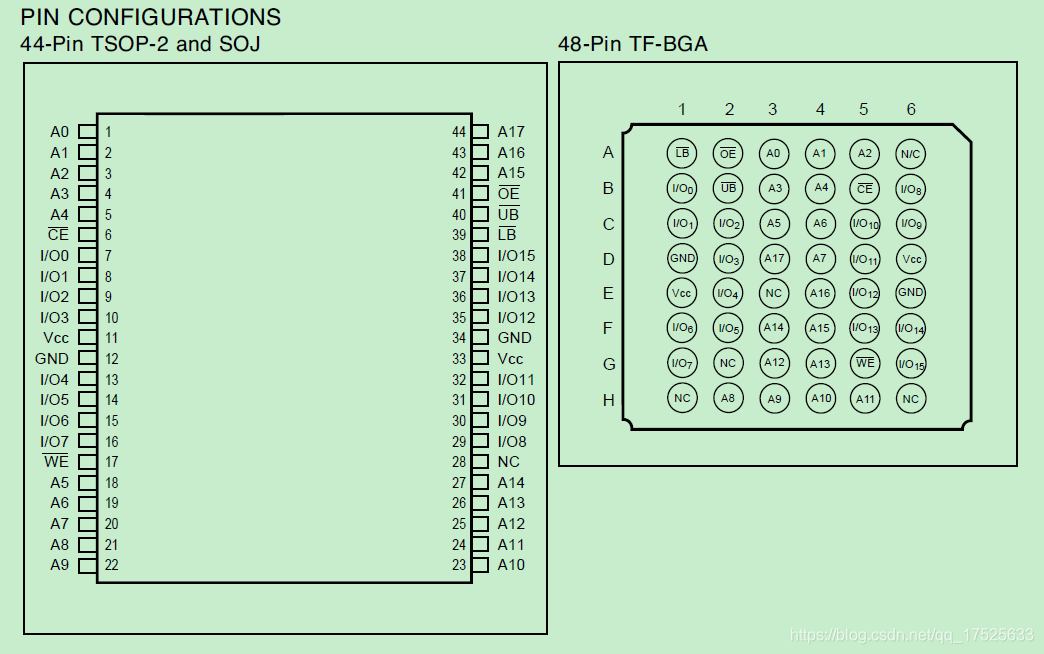

25616被封装成JEDEC标准44管脚400mil SOJ和48管脚 6*8TFBGA。

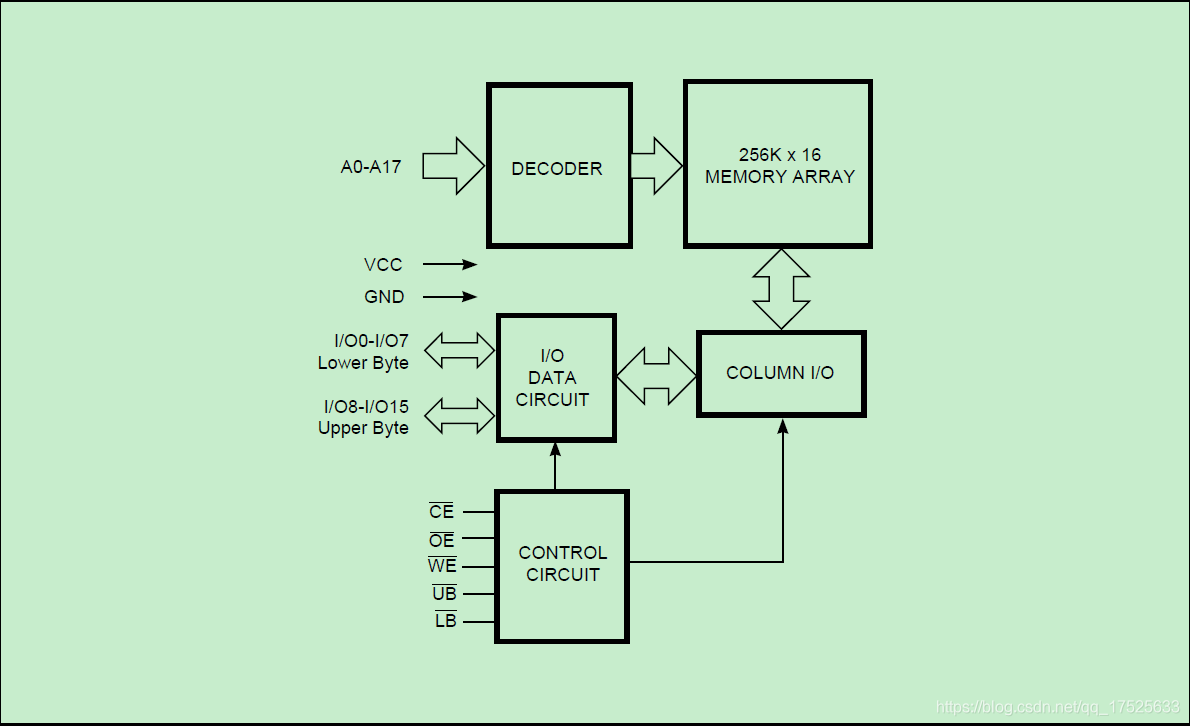

功能块框图

管脚配置图

管脚描述

| A0-A17 | 地址输入 |

|---|---|

| I/O0-I/O15 | 数据输入输出 |

| CE‾\rm{\overline{CE}}CE | 芯片使能输入 |

| OE‾\rm{\overline{OE}}OE | 输出使能输入 |

| WE‾\rm{\overline{WE}}WE | 写入使能输入 |

| LB‾\rm{\overline{LB}}LB | 低字节控制(I/O0~I/O7) |

| UB‾\rm{\overline{UB}}UB | 高字节控制(I/O8~I/O15) |

| NC | 无连接 |

| VCC | 电源 |

| GND | 地信号 |

真值表

| 状态 | WE‾\rm{\overline{WE}}WE | CE‾\rm{\overline{CE}}CE | OE‾\rm{\overline{OE}}OE | LB‾\rm{\overline{LB}}LB | UB‾\rm{\overline{UB}}UB | IO0~IO7 | IO8~IO15 | VCC |

|---|---|---|---|---|---|---|---|---|

| 未被选 | X | H | X | X | X | 高阻 | 高阻 | ISB1,ISB2 |

| 输出禁止 | H X |

L L |

H X |

X H |

X H |

高阻 | 高阻 | ICC |

魔乐社区(Modelers.cn) 是一个中立、公益的人工智能社区,提供人工智能工具、模型、数据的托管、展示与应用协同服务,为人工智能开发及爱好者搭建开放的学习交流平台。社区通过理事会方式运作,由全产业链共同建设、共同运营、共同享有,推动国产AI生态繁荣发展。

更多推荐

已为社区贡献3条内容

已为社区贡献3条内容

所有评论(0)